Variable Waveform Driver and Receiver for Sonic Probe

Variable Waveform Driver and Receiver for Sonic Probe. Group 43 Matt Klug, Jon Reeg, and Maurice Hoang TA: Aaron Rosenberg Spring 2014. Introduction and Objectives Features and Benefits Block Diagram Power System User Interface Waveform Generation Future Work Q&A. Overview.

Variable Waveform Driver and Receiver for Sonic Probe

E N D

Presentation Transcript

Variable Waveform Driver and Receiver for Sonic Probe Group 43 Matt Klug, Jon Reeg, and Maurice Hoang TA: Aaron Rosenberg Spring 2014

Introduction and Objectives • Features and Benefits • Block Diagram • Power System • User Interface • Waveform Generation • Future Work • Q&A Overview

Redesign of control circuitry for ultrasonic probes Introduction and Objectives

Benefits: • Intuitive Interface • Portable • User Selection of Waveform and Parameters • Full Frequency Range of Transducer Utilized Features: • LCD display screen to give instructions to the user • 4x4 keypad for the user to input the type of waveform and the parameters Features and Benefits

12/5V Converter Initial Design Buck Converter

12/5V Converter Initial Design Control Circuit Solar Beach Chair Spring 2013

Key Features: • Cost ($4.00) • Allowable Input Current up to 3 A • Efficiency > 96% 12/5V Implemented Design http://www.amazon.com/gp/product/B00A71CMDU/ref=oh_details_o00_s00_i00?ie=UTF8&psc=1

Key Features: • Wide Input Voltage Range of 3.3V to 30 V • Small Output Current ~20mA • Guaranteed Output Voltage of ~200V 12/200V Bias http://www.onsemi.com/pub_link/Collateral/DN05091-D.PDF

Keypad http://imall.iteadstudio.com/im120417001.html

Low cost • No extra buttons • Simple functions given in source code Why this keypad?

LCD Screen http://www.epictinker.com/Nokia-5110-LCD-p/nok5110.htm

Low cost • Compatible with the IBridge 4x4 Keypad Why this LCD Screen?

Arduino Mega ADK http://arduino.cc/en/Main/ArduinoBoardMegaADK?from=Main.ArduinoBoardADK

Arduino Functions • State machine of three waveforms • Receives input from keypad • Calculates signals based off of inputs

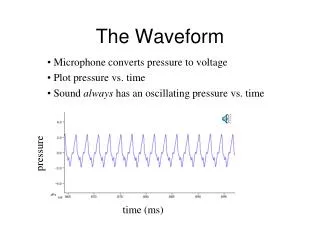

Sample calculations: • Sine wave : incr = (table length / sampling rate) * frequency = (4096 / 800,000) * frequency • Chirp : c_rate = (end_frq-start_frq) / duration incr = (table length / sampling rate) * frequency = (4096 / 800,000) * frequency incr += c_rate Arduino Functions (cont)

FPGA http://papilio.cc/uploads/Papilio/p1sparkfun.jpg

Model used: Papilio ONE • Cheap • Reasonably fast clock (31.25ns) • 48 I/O pins • Open source, large amount of documentation FPGA

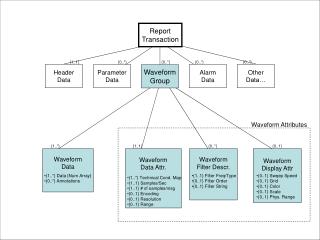

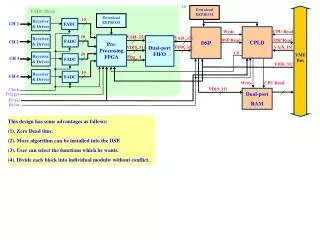

Take the system clock as input • Output an adjusted clock based on an integer factor • i.e. If (i = 160) and (TCLOCKIN = 31.25ns) then (TCLOCKOUT = 5us) • Code taken from: http://vhdlguru.blogspot.com/2011/03/clock-frequency-converter-in-vhdl.html AdderClock and AdderClock2

Reg3 • Parallel load register • Loads the data into INCR only • stores both PHASE and INCR data Adder2 • Adds INCR and PHASE and sense it to the PHASE input on the register Reg3 and Adder2

Essentially a wavetable • Outputs a 12 bit unsigned value based on the PHASE input • Only accepts new values if clk_en is high • Based on code taken from: http://www.alteraforum.com/forum/showthread.php?t=26594 sincos_lut

Outputs control signals to DAC, adjustable in code DAC control

REF191 chip supplies 2.048VDC reference to DAC • DAC outputs a voltage based on the formula: • 2VREF(xDATA/x1000)V • xDATA is 12 bit number in hex from FPGA DAC circuit

Adjusts amplitude of output with simple voltage divider • Buffers output so load impedance has no effect on signal amplitude • Filters DC bias from DAC after buffer POT circuit

Simply separates out the 200VDC needed to bias the transducer from the sound signal received. Receive Circuit

Replace the old circuit entirely by adding a transformer and a 4 high breakdown voltage zener diodes to SEND circuitry • Combine two transducers into one using a diode clamp and program Arduino/FPGA to compensate for pulse/echo system • Reduce size of overall circuitry and put into a plastic box for portability, adding a power switch for ease of use Future Work