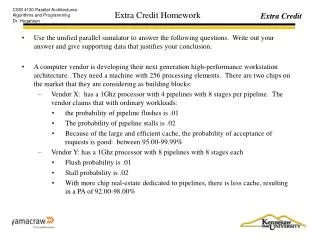

Prolog Extra Credit Homework

Prolog Extra Credit Homework. Basic Boolean Operators in Prolog. or(0,0,0). or(0,1,1). or(1,0,1). or(1,1,1). and(0,0,0) and(0,1,0). and(1,0,0). and(1,1,1). not(0,1). not(1,0). xor(0,0,0). xor(0,1,1). xor(1,0,1). xor(1,1,0). Half-adder:. halfadder(A,B,Carry,Sum):-

Prolog Extra Credit Homework

E N D

Presentation Transcript

Basic Boolean Operators in Prolog or(0,0,0). or(0,1,1). or(1,0,1). or(1,1,1). and(0,0,0) and(0,1,0). and(1,0,0). and(1,1,1). not(0,1). not(1,0). xor(0,0,0). xor(0,1,1). xor(1,0,1). xor(1,1,0).

Half-adder: halfadder(A,B,Carry,Sum):- xor(A,B,Sum),and(A,B,Carry). looks a lot like? xor() and()

Full-adder: or-gate Exercise: Write the prolog rule for a full adder. fulladder(A,B,CarryIn,Sum,CarryOut):- halfadder(A,B,S,C1), halfadder(S,CarryIn,Sum,C2), or(C1,C2,CarryOut).

Programming Problem 1: • Write a prolog program that will combine one half-adder and three full-adders to perform 4-bit arithmetic. add4bits([A3,A2,A1,A0],[B3,B2,B1,B0],[Sum3,Sum2,Sum1,Sum0],CarryOut):- these are lists

Programming Problem 2: A 4-input multiplexer accepts 4 input bits and outputs exactly one of them. The bit to be outputted depends on the values of the control lines - C0 and C1. For example, if C0 = 0 and C1 = 1 then Output = D2.

4-bit Multiplexer Logic: or-gate and-gate complementor multiplex4bits([D3,D2,D1,D0],[C1,C0],Output):- ...