Power-Up Sequence

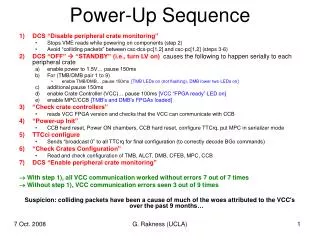

Power-Up Sequence. DCS “Disable peripheral crate monitoring” Stops VME reads while powering on components (step 2) Avoid “colliding packets” between csc-dcs-pc[1,2] and csc-pc[1,2] (steps 3-6)

Power-Up Sequence

E N D

Presentation Transcript

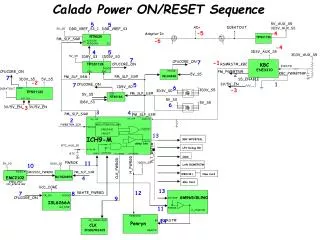

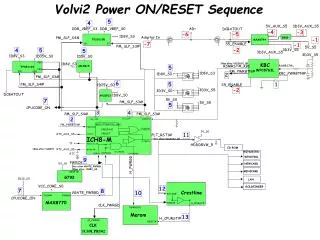

Power-Up Sequence • DCS “Disable peripheral crate monitoring” • Stops VME reads while powering on components (step 2) • Avoid “colliding packets” between csc-dcs-pc[1,2] and csc-pc[1,2] (steps 3-6) • DCS “OFF” “STANDBY” (i.e., turn LV on) causes the following to happen serially to each peripheral crate • enable power to 1.5V… pause 150ms • For (TMB/DMB pair 1 to 9) • enable TMB/DMB… pause 150ms [TMB LEDs on (not flashing), DMB lower two LEDs on] • additional pause 150ms • enable Crate Controller (VCC)… pause 100ms [VCC “FPGA ready” LED on] • enable MPC/CCB [TMB's and DMB's FPGAs loaded] • “Check crate controllers” • reads VCC FPGA version and checks that the VCC can communicate with CCB • “Power-up Init” • CCB hard reset, Power ON chambers, CCB hard reset, configure TTCrq, put MPC in serializer mode • TTCci configure • Sends “broadcast 0” to all TTCrq for final configuration (to correctly decode BGo commands) • “Check Crates Configuration” • Read and check configuration of TMB, ALCT, DMB, CFEB, MPC, CCB • DCS “Enable peripheral crate monitoring” With step 1), all VCC communication worked without errors 7 out of 7 times Without step 1), VCC communication errors seen 3 out of 9 times Suspicion: colliding packets have been a cause of much of the woes attributed to the VCC's over the past 9 months… G. Rakness (UCLA)

CLCT LB FEB RPC TMB RAT RPC RAT Schematic On detector In Towers CSC Peripheral Crate Resistive Plate Chambers Trigger Mother-Board Front End Boards RPC Link Board RPC–ALCT Transition Board ~30m cable SP PC custom back-plane 8-15m SCSI cable • RPC LB data RAT = [(12 pad bits) + BXN (3 bits)] • Scope: RE+1/2 and RE+1/3 (RE+1/1 chambers don’t exist—expected for upgrade) • RPC trigger primitive data to be used by TMB for “ghostbusting” in CSC trigger primitives (eventually) G. Rakness (UCLA)

Parity bit • RPC LB firmware is currently sending… [12 pad bits + 2BXN + 1 parity bit] • The parity bit is computed by the RPC LB based on the rest of the data word in order to make the total number of bits sent be an even number… • The CSC RAT firmware computes the parity bit using the same algorithm as the RPC LB firmware and stores the number of discrepancies in a counter… G. Rakness (UCLA)

RPC LB CSC RAT phase scan Goal: determine the optimal setting of the phase delay at the RAT in order to latch the RPC endcap LB data • Technique: Find the center of the window with 0 parity bit errors… • Change the rpc0_rat_delay setting on the RAT • Reset the parity error counter • Wait for one second • Reads out the counter • The "best" value is in the middle of the window of 0 errors in this counter Example: ME+1/2/3 delay parity counter errors ------- --------------------------- 0 0 1 0 2 0 3 10f 4 ffff 5 ffff 6 42 7 0 8 0 9 0 a 0 b 0 c 0 G. Rakness (UCLA)

Some obvious problems… • delay parity counter errors ------- --------------------------- 0 0 1 0 2 0 3 0 4 0 5 0 6 0 7 0 8 0 9 0 a 0 b 0 c 0 • All ME+1/1 (chambers don’t exist…) • ME+1/2/25 • delay parity counter errors ------- ------------------------------ 0 ffff 1 ffff 2 ffff 3 ffff 4 ffff 5 ffff 6 ffff 7 ffff 8 ffff 9 ffff a ffff b ffff c ffff • ME+1/2/2 • ME+1/3/7, ME+1/3/8 G. Rakness (UCLA)

Number of chambers with parity bit errors vs. RPC-RAT delay Setting used for data until Friday 3 October… G. Rakness (UCLA)

Broken up by “Type” • 49 chambers of Type “A” and “B” would work OK with delay = 11 • Value of 4-5 is best to avoid… G. Rakness (UCLA)

Type “C” are pesky • 19 chambers of type “C” come in clumps • Have asked the RPC colleagues for input… • Have set delay value = 11 for current running… G. Rakness (UCLA)

RAT-TMB phase determination One delay per TMB/RAT (no RPC needed) • Send fixed pattern from RAT to TMB in “sync-mode” • Read RAT 80MHz demux registers at TMB • Compare 19-bits of data read to pattern expected ************************** ** TMB-RAT delay results * ************************** rpc_delay bad data count --------- -------------- 0 10f3d 1 1292c 2 1292c 3 1292c 4 1292c 5 1292c 6 74ac 7 0 8 0 9 0 a 0 b 0 c 2f7 ----------------------------------------------- Window = 0 is 5 channels wide, from 7 to 11 => BEST DELAY VALUE (window 0) = 9 <= ----------------------------------------------- • CONCLUSIONS: • Window Centroid • Default value set at TMB power-up • Width of window ~10ns G. Rakness (UCLA)

To do • Analyze RPC data being taken now… • Set RPC “posneg” bit and do scans again • “Monster event” integration with Global DAQ G. Rakness (UCLA)