V cc

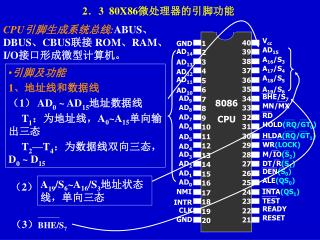

V cc. 40. GND. 1. AD 15. AD 14. 39. 2. A 16 /S 3. 38. AD 13. 3. A 17 /S 4. 引脚及功能 1 、地址线和数据线 ( 1 ) AD 0 ~ AD 15 地址数据线 T 1 :为地址线, A 0 ~A 15 单向输出三态 T 2 —T 4 :为数据线双向三态, D 0 ~ D 15. 37. 4. AD 12. A 18 /S 5. AD 11. 36. 5. 35. A 19 /S 6. 6. AD 10. BHE/S 7. AD 9. 34. 7.

V cc

E N D

Presentation Transcript

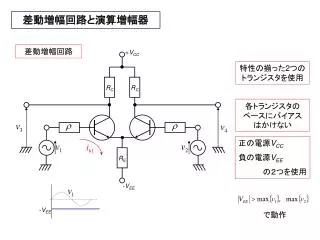

Vcc 40 GND 1 AD15 AD14 39 2 A16/S3 38 AD13 3 A17/S4 • 引脚及功能 • 1、地址线和数据线 • (1)AD0 ~ AD15地址数据线 • T1:为地址线,A0~A15单向输出三态 • T2—T4:为数据线双向三态,D0 ~ D15 37 4 AD12 A18/S5 AD11 36 5 35 A19/S6 6 AD10 BHE/S7 AD9 34 7 RD 8086 CPU MN/MX AD8 33 8 AD7 32 9 AD6 31 10 HOLD(RQ/GT0) HLDA(RQ/GT1) 30 AD5 11 29 12 AD4 WR(LOCK) AD3 M/IO(S2) 28 13 AD2 DT/R(S1) 27 14 DEN(S0) AD1 26 15 BHE/S7 INTA(QS1) ALE(QS0) A19/S6~A16/S3地址状态线,单向三态 AD0 25 16 (2) TEST NMI 24 17 23 18 INTR READY CLK 22 19 RESET GND 21 20 (3) 2.3 80X86微处理器的引脚功能 CPU引脚生成系统总线:ABUS、DBUS、CBUS联接ROM、RAM、I/O接口形成微型计算机。

=0,最大工作模式 =1,最小工作模式 Vcc 40 GND 1 AD15 AD14 39 2 A16/S3 38 AD13 3 A17/S4 37 4 AD12 A18/S5 AD11 36 5 (2)NMI ,不可屏蔽中断,单向、输入 CPU不可以进行屏蔽。执行完本条指令后控制转移到中断服务程序。(如掉电等特殊情况) 35 A19/S6 6 AD10 RD BHE/S7 AD9 34 7 8086 CPU MN/MX AD8 33 8 AD7 32 MN/MX 9 HOLD(RQ/GT0) AD6 31 10 HLDA(RQ/GT1) 30 AD5 11 WR(LOCK) 29 12 AD4 AD3 M/IO(S2) 28 13 (3)INTR,可屏蔽中断, 单向、输入。 只有当IF=1时外设的中断请求才可能被响应。当IF=0时所有的中断申请均不能响应。 AD2 DT/R(S1) 27 14 DEN(S0) AD1 26 15 INTA(QS1) TEST ALE(QS0) AD0 25 16 (1)MN/MX工作模式信号 NMI 24 17 23 18 INTR READY CLK 22 19 RESET GND 21 20 2.3 80X86微处理器的引脚功能 2、控制总线

Vcc 40 GND 1 AD15 AD14 39 2 A16/S3 38 AD13 3 (5) 读操作有效信号,单向、输出 A17/S4 37 4 AD12 完成存贮器和I/O读取操作。 A18/S5 AD11 与 36 5 =0,读I/O设备 =0,I/O设备操作 =0 35 A19/S6 6 AD10 M/IO M/IO M/IO RD BHE/S7 AD9 34 7 8086 CPU MN/MX =1 =0,读存贮器 AD8 33 8 =1,存贮器操作 单向输出,读操作有效信号,完成存贮器和外设的读取操作。 AD7 32 9 HOLD(RQ/GT0) AD6 31 10 HLDA(RQ/GT1) 30 AD5 11 (6)CLK 主时钟引入线4.77M~10M为8088和8086的主时钟。 WR(LOCK) 29 12 AD4 AD3 M/IO(S2) 28 13 AD2 DT/R(S1) 27 14 DEN(S0) AD1 26 M/IO 15 INTA(QS1) TEST ALE(QS0) (7)RESET复位信号,单向、输入 AD0 25 16 NMI 24 17 RD RD RD 23 18 INTR READY (8)READY准备好信号,单向、输入 CLK 22 19 RESET GND 21 20 (4)

(9) 测试信号,单向、输入。 Vcc 40 GND 1 AD15 AD14 39 2 A16/S3 38 AD13 3 A17/S4 37 4 AD12 A18/S5 (11) 写操作有效信号,单向、输出 AD11 36 5 35 A19/S6 6 AD10 =0,写I/O设备 与 完成存贮器和I/O写取操作。 M/IO RD BHE/S7 =0 AD9 34 7 8086 CPU MN/MX AD8 33 8 AD7 32 9 =1 =0,写存贮器 HOLD(RQ/GT0) AD6 31 10 INTA HLDA(RQ/GT1) 30 AD5 11 WR(LOCK) 29 12 AD4 AD3 M/IO(S2) (12) 可屏蔽中断应答信号。单向、输出 28 13 TEST AD2 DT/R(S1) 27 14 DEN(S0) AD1 26 M/IO 15 INTA(QS1) TEST ALE(QS0) (13)ALE 地址锁存信号 ,单向,输出。 T1:锁存AD0~AD15上的地址信号,经 锁存器得到A0~A19地址总线。 AD0 25 16 NMI 24 17 WR WR WR 23 18 INTR READY CLK 22 19 RESET GND 21 20 (10)GND、VCC VCC=+5V,GND=0V 电源的正负极。 • 最小工作模式下的控制信号。

(15) 数据收发信号 ,单向,输出。 读操作,由M/IO到CPU =0 Vcc 40 GND 1 AD15 AD14 39 2 A16/S3 38 AD13 3 =1 写操作,由CPU到M/IO A17/S4 37 4 AD12 A18/S5 AD11 36 5 35 A19/S6 6 AD10 DT/R DT/R RD BHE/S7 AD9 34 (16)HOLD总线请求,单向、输入。 总线请求部件发出HOLD=1,产生一个总线请求。 (17)HLDA总线应答,单向、输出。 7 8086 CPU MN/MX AD8 33 8 AD7 32 9 HOLD(RQ/GT0) AD6 31 10 DEN HLDA(RQ/GT1) 30 AD5 11 WR(LOCK) 29 12 AD4 AD3 M/IO(S2) 28 13 AD2 DT/R(S1) 27 14 DEN(S0) AD1 26 15 INTA(QS1) TEST ALE(QS0) AD0 25 16 NMI 24 17 23 18 INTR READY CLK 22 19 RESET GND 21 20 (14) 可数据允许 ,单向,输出。

Vcc 40 GND 1 AD15 AD14 39 2 A16/S3 38 AD13 3 A17/S4 37 4 AD12 A18/S5 AD11 36 5 QS1 QS0 0 0 无操作 0 1 第一字节 1 0 队列空 1 1 后续字节 35 A19/S6 6 AD10 RD BHE/S7 AD9 34 7 8086 CPU MN/MX AD8 33 8 AD7 32 9 HOLD(RQ/GT0) AD6 31 10 HLDA(RQ/GT1) 30 AD5 11 WR(LOCK) 29 12 AD4 AD3 M/IO(S2) 28 13 AD2 DT/R(S1) 27 14 DEN(S0) AD1 26 15 INTA(QS1) TEST ALE(QS0) AD0 25 16 NMI 24 17 23 18 INTR READY CLK 22 19 RESET GND 21 20 最大工作模式下的控制信号。 (1)QS0、QS1,指令队列状态,单向、输出。

机器周期状态,输出三态 (2) Vcc 40 GND 1 AD15 AD14 39 2 A16/S3 38 AD13 3 A17/S4 37 4 AD12 A18/S5 AD11 36 5 35 A19/S6 6 AD10 RD BHE/S7 AD9 34 7 8086 CPU MN/MX AD8 33 8 0 0 0 中断响应 0 0 1 读I/O 0 1 0 写I/O 0 1 1 暂停 1 0 0 取指 1 0 1 读存储器 1 1 0 写存储器 1 1 1 无效 AD7 32 9 HOLD(RQ/GT0) AD6 31 10 HLDA(RQ/GT1) 30 AD5 11 WR(LOCK) 29 12 AD4 AD3 M/IO(S2) 28 13 AD2 DT/R(S1) 27 14 DEN(S0) AD1 26 15 INTA(QS1) TEST ALE(QS0) AD0 25 16 NMI 24 17 S2、S1、S0 S2、S1、S0 23 18 INTR READY CLK 22 19 RESET GND 21 20 最大工作模式下的控制信号。 提供当前总线机器状态信号作为8288的输入信号编码,由8288输出控制信号。

总线请求信号, 输出、输入。 (4) Vcc 40 GND 1 AD15 AD14 39 2 (3) 总线封锁信号, 输出。 A16/S3 38 AD13 3 A17/S4 37 4 AD12 A18/S5 AD11 36 5 35 A19/S6 6 AD10 RD BHE/S7 AD9 34 7 8086 CPU MN/MX AD8 33 8 AD7 32 9 HOLD(RQ/GT0) AD6 31 10 HLDA(RQ/GT1) 30 AD5 11 WR(LOCK) 29 12 AD4 AD3 M/IO(S2) 28 13 LOCK AD2 DT/R(S1) 27 14 DEN(S0) AD1 26 15 INTA(QS1) TEST ALE(QS0) AD0 25 16 NMI 24 17 23 18 INTR READY CLK 22 19 RQ/GT0 RQ/GT1 RESET GND 21 20 最大工作模式下的控制信号。

3、8086 CPU 8088 CPU BHE/S7 AD8~AD15 M/IO(S2) IO/M(S2) A8~A15 SS0(HIGH) Vcc Vcc 40 40 GND 1 GND 1 AD15 A15 AD14 A14 39 39 2 2 A16/S3 A16/S3 38 38 AD13 3 A13 3 A17/S4 A17/S4 37 37 4 4 AD12 A12 A18/S5 A18/S5 AD11 A11 36 36 5 5 35 A19/S6 35 A19/S6 6 6 AD10 A10 RD RD BHE/S7 AD9 A9 SS0(HIGH) 34 34 7 7 MN/MX 8086 CPU 8088 CPU MN/MX AD8 A8 33 33 8 8 AD7 AD7 32 32 9 9 HOLD(RQ/GT0) HOLD(RQ/GT0) AD6 AD6 31 31 10 10 HLDA(RQ/GT1) HLDA(RQ/GT1) 30 30 AD5 11 AD5 11 WR(LOCK) WR(LOCK) 29 29 12 12 AD4 AD4 M/IO(S2) IO/M(S2) AD3 AD3 28 28 13 13 AD2 DT/R(S1) AD2 DT/R(S1) 27 27 14 14 DEN(S0) DEN(S0) AD1 AD1 26 26 15 15 INTA(QS1) INTA(QS1) ALE(QS0) ALE(QS0) TEST TEST AD0 AD0 25 25 16 16 NMI NMI 24 24 17 17 23 23 18 18 INTR INTR READY READY CLK CLK 22 22 19 19 RESET RESET GND GND 21 21 20 20

第6章 输入/输出 6.2简单的输入/输出接口芯片 信号放大、隔离锁存,与系统总线的信号、时序相适应。常用数据缓冲器、收发器和锁存器。 74系列器件是TI(美国德州仪器)公司生产的中小规模数字集成电路。从功能和速度上分为如下几类。 74XXX 标准TTL 74LXXX 低功耗TTL 74SXXX 肖特基型TTL 74LSXXX 低功耗肖特基型TTL 74ALSXXX 高性能型TTL 74FXXX 高速性TTL 同编号(XXX)其逻辑功能完全一样。

第6章 输入/输出 锁存器74LS373 1 20 Vcc 1Q 8Q 19 2 三态驱动、8D锁存器 1D 18 3 8D 1D 2D D 17 4 7Q 8输入端:1D~8D 8输出端:1Q~8Q 2个控制端:G、OE 1Q 2Q 373 16 5 7D 3Q 2D 15 6 D 6Q 3D 14 7 6D 2Q 4Q 13 8 5Q 3D D 4D 9 12 5D 3Q GND 10 G 11 4D D 4Q 1D 1Q 5D D 2D 2Q 5Q 3D 3Q 4Q 6D 4D D 5Q 5D 6Q 6Q 6D 0 输出三态打开锁存器中的数据输出到Q 7D 7Q D 7D Q Q Q Q Q Q Q Q 8Q 8D 7Q 1 D中的数据打入锁存器 OE OE G G G G G G G G G = 8D D G= 8Q 1 输出高阻态 G 0 数据保存 OE OE 6.2简单的输入/输出接口芯片

第6章 输入/输出 244 VCC 1 20 1A1 19 2 18 2Y4 1Y1 3 17 1A2 2A4 4 1Y2 2Y3 16 5 1A3 2A3 15 6 14 2Y2 1Y3 7 1,1A与1Y 输出高阻态 1,2A与2Y 输出高阻态 1A4 13 8 2A2 = = 2Y1 9 12 1Y4 0,2A与2Y有效驱动 0,1A与1Y有效驱动 GND 10 11 2A1 1A1 1Y1 1A2 1Y2 1Y3 1A3 1A4 1Y4 2A1 2Y1 2A2 2Y2 2A3 2Y3 2A4 2Y4 2G 1G 1G 2G 1G 2G 6.2简单的输入/输出接口芯片 缓冲器 74LS244 三态驱动、8位缓冲、驱动器。 8输入端:1A1~1A4 、2A1~2A4 8输出端:1Y1~1Y4 、2Y1~2Y4 2个控制端:

第6章 输入/输出 A1 B1 A2 B2 B3 A3 A4 B4 245 A5 B5 =1 A→B A6 B6 A7 B7 =0 B→A A8 B8 =1 A到B驱动有效 DT/R DT/R DT/R =0 G G B到A驱动有效 =0 =1 A之间B为高阻态 2G 1G 6.2简单的输入/输出接口芯片 数据收发器 74LS245 三态驱动、8位双向缓冲、驱动器。 A边 8输入、出端:A1~A8 B边 8输入、出端:B1~B8 数据收发方向控制 三态输出控制

课后作业: 1. P76 2.4 2.8