Lab Practicing in Studying the Assembly Languages and Computer Architecture

560 likes | 726 Views

Lab Practicing in Studying the Assembly Languages and Computer Architecture. b y Mile K. Stoj čev 1 , Tatjana R. Stanković 1 and Predrag V. Krtolica 2. 1 Faculty of Electronic Engineering in Ni š, University of Ni š 2 Faculty of Science and Mathematics in Ni š , University of Ni š. Outlines.

Lab Practicing in Studying the Assembly Languages and Computer Architecture

E N D

Presentation Transcript

Lab Practicing in Studying the Assembly Languages and Computer Architecture by Mile K. Stojčev1, Tatjana R. Stanković1 and Predrag V. Krtolica2 1Faculty of Electronic Engineering in Niš, University of Niš 2Faculty of Science and Mathematics in Niš, University of Niš

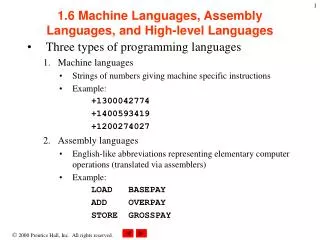

I. Introduction Lab exercises Programming oriented Logic design oriented DOS (4 exercises) VHDL description of three stage pipelined system Intel 80x86 (15 exercises) MIPS (5 exercises) Six more exercises about VHDL design, in perspective

Programming oriented lab exercises • The best way to learn programming is programming it self! • Two very popular paradigms of the processor architecture in computer science curricula are: • MIPS processor, • Intel 80x86 microprocessor family. • For writing and running programs in assembly language of Intel microprocessor family we use MASM 6.11. • But, MIPS workstations are expensive, so we use a PCSpim simulator, created by J. R. Larus [6].

II. Review of the exercises • We have 28 exercises developed. • Exercises 1-4 are devoted to DOS and related topics. • Exercises 5-19 are devoted to Intel 80x86 family and PWB editor. • Exercises 20-24 are devoted to MIPS programming and corresponding simulator. • Exercises 25-28 are devoted to VHDL.

General structure and usage of lab exercises • The exercise material contains brief guidelines for the exercise, followed by one or more practical tasks. • At the end of every exercise there is a set of questions, covering the underlying topic, which students should answer. • The described exercises are part of subjects Microprocessor systems (2075) and Microcomputer systems (6107) at Faculty of Electronic Engineering in Niš, University of Niš. • These exercises are going to be introduced as a part of Computer systems (1231) subject in III and IV semester of informatics course, at Department of Mathematics and Informatics, Faculty of Science and Mathematics in Niš, University of Niš.

Problem definition from a part of Exercise 4 Let us suppose that a small program is displaying a message “Hi, colleagues”. To display a character string, DOS function call 9 is used. This function requires that register pair DS:DX points to stringand AH register contains 09H, before INT 21H instructionis executed. This instruction allows access to DOS functions. Note that character string must be ended with $. In the following example the character string is stored from address 1000:0100, and program is stored from address 1000:0000:

Example program from a part of Exercise 4 -A1000:0100 1000:0100 DB ’Hi, colleagues$’ 1000:010E -A1000:0000 1000:0000 MOV AX,1000 1000:0003 MOV DS, AX 1000:0005 MOV AH, 9 1000:0007 MOV DX, 100 1000:000A INT 21 1000:000C INT 3 -

Task from a part of Exercise 4 Step 5:Using the command U (Unassemble) check if the program is stored in memory, i.e. display it using DEBUG command: U1000:0000 If the program is correctly stored, its execution is possible.

What we get? • These four exercises should make the students totally independent for work in DOS environment. • Students were taught about the most frequent DOS commands, including batch files commands, and about setting a computer defining contents of autoexec.bat and config.sys. • Students are introduced in editor EDIT and DEBUG program. • Their knowledge about DOS and related topics can be estimated from medium to advanced.

Example program from a part of Exercise 6 CODE SEGMENT ‘code’ ASSUME CS: CODE MAIN PROC FAR MOV AH,02H MOV DL,’A’ ; display A INT 21H MOV DL,’B’ ; display B INT 21H MOV DL,’C’ ; display C INT 21H MOV AX,4C00H ; return to DOS INT 21H MAIN ENDP ; end of MAIN CODE ENDS ; end of program segment END MAIN

Note for example from a part of Exercise 6 Note that that the value 02H is stored in AH register only once, in the begining of the program. Further calls for displying an ASCII character need not to load 02H in AH. Only contents of AL is changed.

Task from a part of Exercise 6 Step 1:Using PWB, type the program from Example 6-1 and check if it runs correctly. Now, rewrite the program to display word ELEF. Do not forget that contents of DL register is reserved by DOS INT 21H function call (in DL the current character to display must be stored).

What we get? • By completing these exercises, the students become capable of writing and running programs for Intel microprocessor family. • Their knowledge in assembly programming is medium graded, and allows them to be independent in future programming tasks. • Students should understand better the architecture of computers based on Intel microprocessor family, and they should know more about overall computer operation.

In the following we will present the complete layout of exercise 21 named MIPS instruction set, pseudoinstructions.

Lab exercise 21 MIPS instruction set, pseudoinstructions Introduction For this lab exercise, the experience in PCSpim simulator usage from the previous exercise is needed. Also, knowledge about basic instruction set for microprocessor MIPS, available in [1] and [2] (chapters 4 and 5), is necessary. Inputting and running the shorter sequences in MIPS assembly language, a student should confirm his/hers knowledge about the instruction execution mechanism through the effects of this execution. Also, the notion of pseudoinstructions is introduced, and their importance, as well. By the example of two vectors comparison, the student is introduced to the fundamental conventions of assembly programs writing.

Task Introduce yourself to basic instruction and functional instruction sequences which correspond to HLL statements. Make an overview of complete program, that is, the ways of data declaration (data segment) and program declaration (text segment).

Working procedure Step 1: Let A be a 100 elements vector, and g = 1500 and h = 1900 are variables. The variables g and h should be stored in registers $s1 and $s2, respectively, the vector A base address in $s3, while the result should be stored at location of variable g. Firstly, in Notepad editor type data declaration as the following: .data a: .word 0x00001234 0x00005678 0x00009abc 0x0000def0 0x12340000 .word 0x56780000 0x9abc0000 0xdef00000 0x00123400 0x00567800 .word 0x009abc00 g: .word 1500 h: .word 1900 The following C statement g = h + A[8]; translated to MIPS assembly language has a form:

main: la $s3,a # address of a[0]$s3 lw $s2,h($zero) # h$s2 lw $t0,32($s3) # a8$t0 add $s1,$s2,$t0 # g = $s1 = h + a[8] sw $s1,g($zero) # gG j $ra In the same file, after the data, enter directive .globl main, and, after that, the sequence beginning at label main. Save the program as pr_1.asm in PCSpim directory. Run this program step by step (using F10 key). Note the effects of every instruction execution, and write them in source file as a comment. Which of the instructions are the pseudoinstructions? Which is the hexadecimal value of the result?

Step 2: Using the same text editor as in Step 1, type the following MIPS assembly code for comparisons of two integer vectors. How many values should be tested in each vector? What is the form of the result and where comparison result is stored? Run the program and write, as the comments, the effects of every instruction in the source file.

.text .globl main main: subu $sp, $sp, 32 sw $ra, 20($sp) sw $fp, 16($sp) addu $fp, $sp, 32 lw $a0, size la $a1, array1 la $a2, array2 jal compare lw $ra, 20($sp) lw $fp, 16($sp) addu $sp, $sp, 32 j $ra # a0 = vector length # a1 = base address of vector 1 # a2 = base address of vector 2 compare: subu $sp, $sp, 32 sw $ra, 20($sp) sw $fp, 16($sp) addiu $fp, $sp, 32 loop: beq $a0, $0, done lw $t0, 0($a1) lw $t1, 0($a2) bne $t0, $t1, no addiu $a1, $a1, 4 addiu $a2, $a2, 4 addi $a0, $a0, -1 b loop no: ori $v0, $0, 1 b return done: ori $v0, $0, 0 return: lw $31, 20($sp) lw $fp, 16($sp) addu $sp, $sp, 32 j $31 .data size: .word 5 array1: .word 1 2 3 4 5 array2: .word 1 2 3 4 5

Step 3: As we noted in Step 1, there are some assembly instructions called pseudoinstructions. The assembler translates them in the form of the shorter sequences of instructions from basic set (bar-code). After that, they are translated in machine code. Using the descriptions of basic assembly instructions, find out the bar-code sequences which should replace the following instructions: a) abs, b) mul, c) neg, d) rem, e) rol, f) seq, g) bgeu, h) bgt, and i) ld. Check if PCSpim supports these pseudoinstructions. For supported ones, compare them with your solution.

Questions • Explain the notion of bar-code machine. • By which directive data segment starts, and by which program segment starts? • Find the key instruction in pr_1.asm that fetches the target vector element. What is the index of this element? • Draw a flowchart for two vector comparison example. Mark the program labels on the flowchart. • Observe and point every pseudoinstruction in the given examples.

What we get? • Using PCSpim simulator and MIPS assembly language in these exercises get more skills in MIPS programming, • Also, they get better picture of RISC architecture and parallelism on machine and instruction level.

VHDL ENTITY description of DECODE block ENTITY decode_ent IS PORT ( clock : IN std_logic; command : IN command_type; pd_source1 : IN register_type; pd_source2 : IN register_type; pd_destination : IN register_type; pd_data : IN std_logic_vector (31 downto 0); flush : IN std_logic; d_command : OUT command_type; d_destination : OUT register_type; d_source1 : OUT register_type; d_source2 : OUT register_type; d_data : OUT std_logic_vector (31 downto 0); ); END decode_ent;

Benchmark program from Exercise 26 Load #10051, reg0 Load #1, reg1 Add reg0, reg1, reg2 Sub reg0, reg1, reg3

One of the tasks from Exercise 26 for two groups of students (there are much more group tasks) Modify testbench program code to stimulate predecode block by the following instructions: Group 1: Group 2: Load #183FFA20, reg2 Load #183FFA20, reg5 Load #0210AA18, reg4 Load #0210AA18, reg3 Add reg2, reg4, reg8 Sub reg3, reg5, reg9 Read reg8 Read reg9 Nop Move reg3, reg5 Read reg5

VHDL code for PREDECODE block LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE WORK.pipeline_package.ALL; ENTITY predecode_ent IS PORT ( clock : IN std_logic; inst : IN std_logic_vector (2 downto 0); source1 : IN std_logic_vector (3 downto 0); source2 : IN std_logic_vector (3 downto 0); destination : IN std_logic_vector (3 downto 0); data : IN std_logic_vector (31 downto 0); flush : IN std_logic; command : OUT command_type; pd_source1 : OUT register_type; pd_source2 : OUT register_type; pd_destination : OUT register_type; pd_data : OUT std_logic_vector (31 downto 0); pd_read : OUT std_logic ); END predecode_ent;

continued ARCHITECTURE predecode_arch OF predecode_ent IS BEGIN PROCESS (clock, inst, source1, source2, destination, data, flush) VARIABLE internal_command : command_type := NOP; VARIABLE internal_source1 : register_type := reg0; VARIABLE internal_source2 : register_type := reg0; VARIABLE internal_destination : register_type := reg0; BEGIN IF (clock = '1' AND clock'EVENT) THEN IF (flush = '0') THEN CASE inst IS WHEN "000" => pd_read <= '1'; internal_command := MOVE; WHEN "001" => pd_read <= '1'; internal_command := ADD; WHEN "010" => pd_read <= '1'; internal_command := SUB;

continued WHEN "011" => pd_read <= '1'; internal_command := MUL; WHEN "100" => pd_read <= '1'; internal_command := CJE; WHEN "101" => pd_read <= '0'; internal_command := LOAD; WHEN "110" => pd_read <= '1'; internal_command := READ; WHEN "111" => pd_read <= '0'; internal_command := NOP; WHEN OTHERS => NULL; END CASE;

continued CASE source1 IS WHEN "0000" => internal_source1 := reg0; WHEN "0001" => internal_source1 := reg1; WHEN "0010" => internal_source1 := reg2; WHEN "0011" => internal_source1 := reg3; WHEN "0100" => internal_source1 := reg4; WHEN "0101" => internal_source1 := reg5; WHEN "0110" => internal_source1 := reg6; WHEN "0111" => internal_source1 := reg7; WHEN "1000" => internal_source1 := reg8; WHEN "1001" => internal_source1 := reg9;

continued WHEN "1010" => internal_source1 := reg10; WHEN "1011" => internal_source1 := reg11; WHEN "1100" => internal_source1 := reg12; WHEN "1101" => internal_source1 := reg13; WHEN "1110" => internal_source1 := reg14; WHEN "1111" => internal_source1 := reg15; WHEN OTHERS => NULL; END CASE;

continued CASE source2 IS WHEN "0000" => internal_source2 := reg0; WHEN "0001" => internal_source2 := reg1; WHEN "0010" => internal_source2 := reg2; WHEN "0011" => internal_source2 := reg3; WHEN "0100" => internal_source2 := reg4; WHEN "0101" => internal_source2 := reg5; WHEN "0110" => internal_source2 := reg6; WHEN "0111" => internal_source2 := reg7; WHEN "1000" => internal_source2 := reg8; WHEN "1001" => internal_source2 := reg9;

continued WHEN "1010" => internal_source2 := reg10; WHEN "1011" => internal_source2 := reg11; WHEN "1100" => internal_source2 := reg12; WHEN "1101" => internal_source2 := reg13; WHEN "1110" => internal_source2 := reg14; WHEN "1111" => internal_source2 := reg15; WHEN OTHERS => NULL; END CASE;

continued CASE destination IS WHEN "0000" => internal_destination := reg0; WHEN "0001" => internal_destination := reg1; WHEN "0010" => internal_destination := reg2; WHEN "0011" => internal_destination := reg3; WHEN "0100" => internal_destination := reg4; WHEN "0101" => internal_destination := reg5; WHEN "0110" => internal_destination := reg6; WHEN "0111" => internal_destination := reg7; WHEN "1000" => internal_destination := reg8; WHEN "1001" => internal_destination := reg9;

continued WHEN "1010" => internal_destination := reg10; WHEN "1011" => internal_destination := reg11; WHEN "1100" => internal_destination := reg12; WHEN "1101" => internal_destination := reg13; WHEN "1110" => internal_destination := reg14; WHEN "1111" => internal_destination := reg15; WHEN OTHERS => NULL; END CASE;