제 9 장 PLD 와 FPGA

논리회로설계. 제 9 장 PLD 와 FPGA. 배경. 복잡한 논리회로 구현을 위하여 많은 수의 IC 칩들을 사용하는 경우에 , 필요 공간이 커지고 결함 발생률도 높아지는 문제점을 해결하기 위하여 아래와 같은 IC 칩들을 개발 PLD(Programmable Logic Device) 다수의 게이트들로 이루어진 게이트 배열 (gate array) 을 하나의 IC 칩에 포함시킨 장치 회로 구현 시점에서 게이트 입출력 선들 간의 접속 , 즉 프로그래밍 (programming) 을 통하여 회로 구성

제 9 장 PLD 와 FPGA

E N D

Presentation Transcript

논리회로설계 제9장 PLD와 FPGA

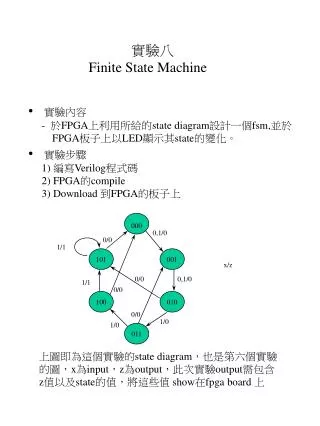

배경 • 복잡한 논리회로 구현을 위하여 많은 수의 IC 칩들을 사용하는 경우에, 필요 공간이 커지고 결함 발생률도 높아지는 문제점을 해결하기 위하여 아래와 같은 IC칩들을 개발 • PLD(Programmable Logic Device) • 다수의 게이트들로 이루어진 게이트 배열(gate array)을 하나의 IC 칩에 포함시킨 장치 • 회로 구현 시점에서 게이트 입출력 선들 간의 접속, 즉프로그래밍(programming)을 통하여 회로 구성 • FPGA(Field Programmable Gate Array) • 게이트 배열뿐 아니라, 내부 상호연결망 및 다수의 입출력(I/O) 블록들도 포함하는 대규모 IC 칩

9.1 PLD의 개요 • PLD의 일반적인 조직 • AND 배열(AND array) : 입력 변수들에 대한 곱의 항(product term)을 구현 • OR 배열(OR array) : AND 배열의 출력(곱의 항)들에 대한 합(sum) 연산을 구현 • PLD의 프로그래밍(programming): 신호 입력 선들과 게이트 입력 선들 간의 교차점을 접속함으로써, 원하는 회로를 구현하는 과정

[예] 2-input 2-outputPLD 아래의 두 부울 함수 들을 PLD로 구현(프로 그래밍 )한 결과 F = A'B + AB' G = AB + A'B'

프로그래밍 과정 • 구현 방법: 접속되지 않는 신호선들의 교차점에 위치한 퓨즈(fuse)들을 단절(open)시킴 [예] AND 배열에서 F = AB 의 구현

PLD의 유형(I) • PROM(Programmable Read-Only Memory): 입력 신호들이 인가되는 AND 배열은 연결 상태가 고정되어 있으며, 출력을 발생하는OR 배열은 퓨즈를 이용하여 프로그래밍 할 수 있도록 구성된 PLD

PLD의 유형 (II) • PAL(Programmable Array Logic): 입력 신호들이 인가되는 AND 배열은 프로그래밍 할 수 있도록 구성되며, 출력을 발생하는 OR 배열은 연결 상태가 고정되도록 구성된 PLD

PLD의 유형 (III) • PLA(Programmable Logic Array): 입력 신호들이 인가되는 AND 배열과 출력을 발생하는OR 배열 모두가 프로그래밍 할 수 있도록 구성되는 PLD

9.2 PROM을 이용한 회로 구현 • PROM의 초기 상태AND 배열: 고정(8개의 SOP형출력들을 발생) OR 배열: 프로그래밍 가능(초기에는모든 교차점들이 접속된 상태)

회로 구현의 예 [예] 3-input, 4-outputPROM을 이용하여 아래의 SOP형 부울 함수들을 구현하라

PROM을 이용한 회로 구현 (계속) • PROM을 이용하여 구현되는 부울 함수에서는모든 항들이 정규형(canonical form)으로 표현되어야 함 • 입력단의 AND 배열에서 각 게이트로 세 개의 입력 신호들이 고정적으로 접속되어 있기 때문 • PROM (그림 9-5)의 AND 배열: 3x8 디코더 회로와 동일 8x4비트 기억장치로 사용 가능 • 입력 신호들(A,B,C): 기억장치 주소(0~7번지) • OR 배열: 각 기억 장소에 저장된 데이터 • OR 게이트 출력들: 데이터 출력

PROM을 이용한 회로 구현 (계속) • PROM의 삭제: 저장된 내용을 원상 복귀시키는 동작 • 방법: 퓨즈 부분에 자외선을 20~30분 동안 비추면 단절된 퓨즈들이 재생되어 접속 상태를 복구 • 삭제된 PROM은 다시 프로그래밍을 통하여 다른 데이터 저장 가능 삭제 가능한 PROM(erasable PROM: EPROM) • EEPROM(electrically erasable PROM): 전기적으로 삭제 가능한 PROM

9.3 PAL(programmable array logic)을 이용한 회로 구현 • PAL의 초기 상태AND 배열: 프로그래밍 가능 (초기에는모든 교차점들이 접속된 상태) OR 배열: 고정 • 3-input 4-output PAL의예

회로 구현의예 [예] 아래의 부울 함수들을 4-input 4-output PAL을 이용하여 구현하라

PAL을 이용한 회로 구현 (계속) [예] 5-input 3-output PAL을 이용한 4-변수 부울 함수들의 구현 (외부 접속을 이용하는 사례)

PAL을 이용한 회로 구현 (계속) • 상용 PAL 칩들의 예 (National Semiconductor사 제품) • 10H8 : 10개의 입력 단자들과 8개의 출력 단자들을 가진 PAL • 14L4 : 14개의 입력 단자들과 4개의 출력 단자들을 가진 PAL • GAL(generic array logic): AND 배열의 각 교차점에퓨즈 대신에 다시 연결 상태를 복구시킬 수 있는 물질을 이용하여 재프로그래밍 가능한 PAL(reprogrammable PAL)

PAL을 이용한 회로 구현 (계속) • 순차형 PAL(sequential PAL): 순차회로구현에 사용될 수 있는 PAL [예] 16R4 순차형 PAL : 16개의입력단자들과 4개의 D플립-플롭들 및 그 출력 단자들로 구성

9.4 PLA를 이용한 회로 구현 • PLA(Programmable Logic Array) • PLD들 중에서 가장 융통성(flexibility)이 높음 • AND 배열과 OR 배열의 모든 교차점들이 퓨즈에 의해 접속 프로그래밍을 통하여 회로의 입력단과 출력단을 모두 원하는대로 구성 가능 [예] PLA를 이용하여 아래의 부울 함수들을 구현

PLA를 이용한 조합회로 구현의 예 • BCD-7SEG 디코더(BCD-to-seven-segment decoder) • 7-세그먼트들 중에서 0부터 9까지의 숫자를 디스플레이 하는데 필요한 출력들을 발생해주는 디코더

9.5 CPLD • SPLD(simple programmable logic device) : 적은수의 게이트들로 이루어지는 논리 장치 (예: PAL,PLA) • CPLD(complex programmable logic device) • 큰규모의 회로들을 구현할 수 있도록 여러 개의 SPLD들을 하나의 칩에 포함 • 다수의 SPLD들과 상호연결망(interconnection)으로 구성 • LAB(Logic Array Block): 각 SPLD를 말하며, 기능블록(function block) 혹은 논리 블록(logic block)이라고도 부름 • PIA(Programmable Interconnection Array): LAB들 간의 상호연결망

CPLD (계속) • 입력 신호들 : 해당 LAB으로 인가 • 출력 신호들 : LAB으로부터 발생다른 LAB으로 입력 가능 • LAB의 내부 접속 및 그들 간의 상호 연결을 위한 PIA의 프로그래밍 작업: 컴퓨터 S/W 이용 • 주요 제조회사들: Altera사, Xilinx사, Lattice사,Cypress사 등

9.6 FPGA • FPGA(Field Programmable Gate Array) • CPLD보다 밀도가 더 높음 • CLB(Configurable Logic Block) • FPGA를 구성하는 단위 블록 • LAB보다 구조가 더 단순하지만, 더 많은 수의 CLB들이 칩에 포함됨 • 상호연결망에 의해 매트릭스(matrix) 형태로 접속 • I/O 블록: 입력 및 출력 신호 인터페이스 • 대규모 FPGA: 수 만개의 CLB들 및 기억장치 등이 포함되므로, 소형 마이크로프로세서 구현도 가능

FPGA (계속) • HDL(hardware description language): FPGA의 CLB 내부 연결 및 CLB들 간의 상호연결을 위한 복잡한 작업을 도와주는 프로그램 언어들 • 종류: VHDL, Verilog, ABEL, AHDL 등 • CPLD 제조회사들(Altera사, Xilinx사, Lattice사,Cypress사 등)이 FPGA도 생산하며, 표준 HDL에 해당하는 VHDL 및 Verilog 를 지원하는 S/W 패키지 제공