EMC Models

EMC Models. Summary. Models, what for ? IC Models for EMC Core Model Package model Test-bench models Emission measurements/simulations Immunity measurements/simulations Conclusion. Models – What for ?. IC DESIGNERS WANT TO PREDICT EMC BEFORE FABRICATION. Noise margin.

EMC Models

E N D

Presentation Transcript

Summary Models, what for ? IC Models for EMC Core Model Package model Test-bench models Emission measurements/simulations Immunity measurements/simulations Conclusion

Models – What for ? IC DESIGNERS WANT TO PREDICT EMC BEFORE FABRICATION Noise margin Switching Noise on Vdd • IC designers want to predict power integrity and EMI during design cycle to avoid redesign • EMC models and prediction tools have to be integrated to their design flows • Short time-to-market • Cost of redesign: several million €

Models – What for ? EQUIPMENT DESIGNERS WANT TO PREDICT EMC BEFORE FABRICATION © Siemens Automotive Toulouse • Most of the time, EMC measurements are performed once the equipment is built. • No improvements can be done at conception phase. • Predict EMC performances IC, board, equipment optimizations • However, need of non-confidential IC models (black box models)

Models – What for ? Models Training Design Guidelines GO EMC VALIDATED BEFORE FABRICATION DESIGN Architectural Design Design Entry Design Architect EMC Simulations Compliance ? FABRICATION NO GO EMC compliant

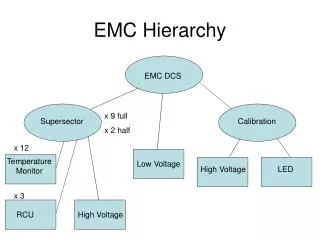

IC models for EMC 101 dipoles Dipoles 101 R,L,C,I ICEM 102 R,L,C,I LEECS 104 R,L,C,I Expo PowerSI EMC MODELS DEPENDS ON THE TARGETED COMPLEXITY, THE LEVEL OF CONFIDENTIALITY OF INFORMATION. Level 100 V(f), 100 Z(f) Equipment V, Z Board Component Physical 106 R,L,C,I spice Complexity low medium high x-high Confidentiality

IC models for EMC EMC Model for the circuit Simulated Emission spectrum Electrical Simulation GENERAL FLOW TO BUILD AN EMC MODEL AND PREDICT EMC PERFORMANCES IEC 62433 Core – I/O Model Package Model Test bench Model Test board Model

IC models for EMC THE IEC 62433 PROJECT

IC models for EMC THE IEC 62433 PROJECT Conducted mode Radiated mode ICEM-CE ICEM-RE Emission IEC 62433-3 IEC 62433 - 2 ICIM-CI ICIM-RI Immunity IEC 62433-4 IEC 62433-5 Impulse immunity IEC 62433-6 Intra-bloc EMC Intra - bloc IEC 62433-7 Research undergoing Standard available Draft of standard

IC models for EMC IEC 62433-2 – “ICEM Conducted Mode” IT IA PDN Package

Core model 1st order assumption : model core activity by triangular waveform current source INTERNAL ACTIVITY (IA) - CURRENT SOURCE EXTRACTION 32 bit processor 500 MHz 16 bit processor 16 MHz Extraction of internal current waveform I I 3 A 100 mA time 62.5 ns time 2 ns

Core model Physical Transistor level (Spice) Interpolated Transistor level Gate level Activity (Verilog) Activity estimation from data sheet Difficult adaptation to usual tools Limited to 1 M devices Huge simulation Limited to analog blocks Simple, not limited Fast & accurate Very simple, not limited Immediate, not accurate Activity 1200 1000 800 Equivalent Current generator 600 Extraction 400 200 0 0 20 40 60 80 100 120 140 time (ns) INTERNAL ACTIVITY (IA) – FROM PHYSICAL TO FIRST-ORDER ESTIMATION In this course

Core model PASSIVE DISTRIBUTION NETWORK (PDN) • Complex network of interconnections, vias and on-chip capacitances • Coupling path for noise through the IC • Require extraction of impedance between Vdd and Vss. • Possible modeling by an equivalent passive model Equivalent passive model Substrate, interconnections metallization Capacitive behavior

Core model IC model Package model Primary resonance Secondary resonance Emission level Frequency ICEM IN IC-EMC - DOUBLE LC SYSTEM ICEM-CE model (IEC 62433-2) Rvdd Lvdd External VDD IA LPackVdd PDN Cd Cb LPackVss IA External VSS Rvss Lvss Low L,C values => High resonant frequency

Core Model Input driver I(V) characteristics Output driver I(V) characteristics Very important for : • I/O switching noise prediction • I/O immunity prediction ADDING IOS - IBIS: INPUT BUFFER I/O SPECIFICATION IBIS file [IBIS Ver] 2.1 [Date] March 17,2011 [File Name] dsPIC33FJ128GP706.ibs [File rev] 1.0 [Component] dsPIC33FJ128GP706 [manufacturer] MICROCHIP [Package] | R_pkg 19.05m 21.2m 16.9m L_pkg 3.025nH 2.61nH 3.44nH C_pkg 0.269pF 0.268pF 0.270pF …

Core Model IC PIN DECLARATION - MODELS

Core Model MODEL DETAILS

Core Model ADDING IOS – SIGNAL TRANSPORT

Package Model CASE STUDY – DSPIC 33F • On-chip decap • Package inductance z11-dspic-vdd_10-vss_9.z

Emission measurement/simulation Core Model Elec. package Model Board Model IC Model DUT Time Domain Simulation Spectrum analyzer FFT of Vanalyzer(t) EMC model Compare spectrums Measurements CONDUCTED/RADIATED EMISSION PREDICTION Simulations Measurements To receiver 1

Emission measurement/simulation ICEM-CE CASE STUDY – DSPIC 33F • Core only

Emission measurement/simulation ICEM-CE CASE STUDY – DSPIC 33F • Core + 16 ADDR • 20dB more noise than core

Emission measurement/simulation H1 H2 I(vss) I(vdd) Magnetic near field scan of a 16 bit microcontroller ICEM-RE – CURRENT DIPOLE THEORY P Vss chip Vdd • Package is the main contributor of the radiated emission of an IC • Magnetic field emission is generated by the flowing of parasitic current through package pins

Emission measurement/simulation Scan Measurements Geometrical package model Core Model Elec. package Model Spectrum analyser Positionning [x,y] Analog Time Domain Simulation H[x,y] at given f, given z Fourier Transform of I(t) H[x,y,z] of I(f) Compare scans ICEM-RE – SIMULATION/MEASUREMENT Scan Simulations

Emission measurement/simulation ICEM-RE – RADIATING DIPOLES PDN IT IA IT

IC models for EMC IEC 62433-4 – “ICIM CONDUCED IMMUNITY” • The package and die impedance act as a coupling path for RF interference (Vin, Iin) to the active blocks, • Filtering effect and/or distortion through the PDN and produce (Vr,Ir). • The IB block describes how the circuit reacts to internal perturbations, and can be represented as (Vout,Iout) for monitoring the failure

IC models for EMC IEC 62433-4 – “ICIM CONDUCED IMMUNITY” IB ICIM – immunity model Package RF disturbance Coupling path Package PDN Monitoring of the failure IC PDN Internal Behaviour IB External pins detection Silicon die PDN = Passive Distribution Network PDN Package Close to ICEM Add Diodes (camp, back-to-back, ESD, EOS) Close to ICEM-CE New!

IC models for EMC + DUT power supply + Internal Behavior (IB) + Perturbation source + Injection device model + Behaviour of sensitive & non-linear parts + Extraction of power injection + DUT input structure model + PCB model + Passive DecouplingNetwork (PDN) IEC 62433-4 – “ICIM CONDUCED IMMUNITY” Coupling path model Injection model Functionnal model RF generator model Susceptibility criterion Power limit Voltage threshold Overcurrent SNR degradation LSB degradation….

Susceptibility measurement/simulation From IBIS Amplitude Coupling path model Vdd input Resonance Time Functional model output clock Vss Disturbance model I/O IC model Supply network Z(f) From ICEM SUSCEPTIBILITY PREDICTION MODEL • ICIM – CE immunity model • Reuse of standard non-confidential models (ICEM, IBIS) • Susceptibility peaks linked with supply network anti-resonances

Susceptibility measurement/simulation Aggressed IC Model (ICEM) Package and IO model (IBIS) RFI and coupling path model (Z(f)) Set RFI frequency IC-EMC Increase V aggressor WinSPICE Increase RFI frequency Time domain simulation Susceptibility threshold simulation Criterion analysis IC-EMC Extract forward power SUSCEPTIBILITY SIMULATION FLOW

Test bench model TEST BENCH MODEL • Electrical model extracted by S parameter measurements and electromagnetic simulations • Test bench models should be generic • Limited frequency range due to influence of parasitic elements, apparition of high order propagation mode TEM Cell DPI capacitance Near-field scan DPI injection

Susceptibility case study DPI ON A 330 OHM LOAD Immunity > Dpi330ohm

Conclusion • EMC models can help earn/save money • Macro-models of ICs include core, I/O and package modeling • The core model is based on current evaluation and on-chip capacitance • The package model is based on RLC • Good prediction of emission and susceptibility up to 2 GHz • Soon, requirements up to 3-10 GHz