Elementary Microarchitecture Algebra

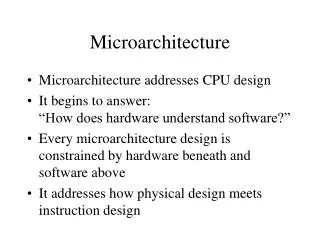

Elementary Microarchitecture Algebra. John Matthews and John Launchbury Oregon Graduate Institute. Hawk Goals. Develop specifications that are clear and concise Simulate the specifications, both concretely and symbolically Formally verify specifications at the source-code level.

Elementary Microarchitecture Algebra

E N D

Presentation Transcript

Elementary Microarchitecture Algebra John Matthews and John Launchbury Oregon Graduate Institute

Hawk Goals • Develop specifications that are clear and concise • Simulate the specifications, both concretely and symbolically • Formally verify specifications at the source-code level

Algebraic Verification • Developed a domain-specific algebra for microarchitectures • Proved equational laws that hold between microarchitecture components • We simplify pipelines using these laws while preserving functional (cycle-accurate) behavior • But clock cycle period may change!

Transactions • Group data and control information together • Transactions - containing destinations, sources, and operations - flow through the model • Decide control locally whenever possible R3 <- Add R1 R2 16 5 11

Example: The SuperSimple Pipeline Reg ALU Reference machine: • Each transaction is completed in one (long) clock cycle • Results are written back to register file on the next clock cycle

Example: The SuperSimple Pipeline Reg ALU Reference machine: R3 <- Add R1 R2 - - -

Example: The SuperSimple Pipeline Reg ALU Reference machine: R3 <- Add R1 R2 R3 <- Add R1 R2 - - - - 5 11

Example: The SuperSimple Pipeline Reg ALU Reference machine: R3 <- Add R1 R2 R3 <- Add R1 R2 R3 <- Add R1 R2 - - - - 5 11 16 5 11

Example: The SuperSimple Pipeline Reg ALU Reference machine: R3 <- Add R1 R2 R3 <- Add R1 R2 R3 <- Add R1 R2 - - - - 5 11 16 5 11 R3 <- Add R1 R2 16 5 11

Example: The SuperSimple Pipeline Reg ALU Reference machine: Reg ALU Pipelined machine:

Verifying SuperSimple • Pipelined machine should behave the same as reference machine, except the pipelined machine has one more cycle of latency Reg ALU Reg ALU

Verifying SuperSimple • We incrementally simplify the pipeline • Use local algebraic laws, each proved by induction over time Reg ALU Reg ALU

Circuit Duplication Law • We can always duplicate a circuit without changing its functional behavior F F F

Retiming the Pipeline • We first move delay circuits forward, using the circuit duplication law Reg ALU Reg ALU

Retiming the Pipeline • We first move delay circuits forward, using the circuit duplication law Reg ALU Reg ALU

Retiming the Pipeline • We first move delay circuits forward, using the circuit duplication law Reg ALU Reg ALU

Time-Invariance Laws • Delay circuits can be moved across time-invariant circuits without changing behavior ALU ALU

Retiming the Pipeline • Apply time-invariance laws to continue moving delay circuits Reg ALU Reg ALU

Retiming the Pipeline • Apply time-invariance laws to continue moving delay circuits Reg ALU Reg ALU

Retiming the Pipeline • Apply time-invariance laws to continue moving delay circuits Reg ALU Reg ALU

Removing Forwarding Logic • The register-bypass laws allow us to remove a bypass circuit on the output of a registerFile Reg Reg Reg Reg

Removing Forwarding Logic • Apply register-bypass law to remove bypass circuit Reg ALU Reg ALU

Removing Forwarding Logic • Apply register-bypass law to remove bypass circuit Reg ALU Reg ALU

Removing Forwarding Logic • Repositioning components Reg ALU Reg ALU

Removing Forwarding Logic • Repositioning components Reg ALU Reg ALU

Removing Forwarding Logic • Repositioning components Reg ALU Reg ALU

Removing Forwarding Logic • Repositioning components Reg ALU Reg ALU

Removing Forwarding Logic • Repositioning components Reg ALU Reg ALU

Removing Forwarding Logic • Repositioning components Reg ALU Reg ALU

Removing Forwarding Logic • Repositioning components Reg ALU Reg ALU

Simplification Complete! • Pipeline has been reduced to reference machine, but delayed by one clock cycle Reg ALU Reg ALU

Simplifying Stalling Pipelines • More complex pipelines often have to stall to resolve hazards or mis-speculation • A stalling pipeline won’t be cycle-accurate with respect to a reference machine • We still simplify as much as possible • Then use other verification techniques on simplified pipeline • Simplified pipeline should be easier to verify

The SomewhatSimple Pipeline • Resolves mem-alu data hazards by stalling • Resolves branch mispredictions by squashing misp ? hazard? ICache Reg ALU Mem Kill

misp ? hazard? ICache Reg ALU Mem Kill Original Pipeline

misp ? hazard? ICache Reg ALU Mem Kill Simplifying pipeline .....

misp ? hazard? ICache Reg ALU Mem Kill Various Retiming Laws Simplifying pipeline .....

misp ? hazard? ICache Reg ALU Mem Kill Various Retiming Laws Simplifying pipeline .....

misp ? hazard? ICache Reg ALU Mem Kill Simplifying pipeline .....

misp ? hazard? ICache Reg ALU Mem Kill Simplifying pipeline .....

misp ? hazard? ICache Reg ALU Mem Kill Simplifying pipeline .....

misp ? hazard? ICache Reg ALU Mem Kill Simplifying pipeline .....

misp ? hazard? ICache Reg ALU Mem Kill Simplifying pipeline .....

misp ? hazard? ICache Reg ALU Mem Kill Simplifying pipeline .....

misp ? hazard? ICache Reg ALU Mem Kill Simplifying pipeline .....

misp ? hazard? ICache Reg ALU Mem Kill Simplifying pipeline .....

misp ? hazard? ICache Reg ALU Mem Kill Simplifying pipeline .....

misp ? hazard? ICache Reg ALU Mem Kill Simplifying pipeline .....

misp ? hazard? ICache Reg ALU Mem Kill Simplifying pipeline .....

misp ? hazard? ICache Reg ALU Mem Kill Simplifying pipeline .....

misp ? hazard? ICache Reg ALU Mem Kill Simplifying pipeline .....