VHDL Presentation

VLSI Design & Reconfigurable Computing ENG*6090(3) Advanced Topics in VHDL Stephen Coe Guangfa Lu Friday, March 07, 2003. VHDL Presentation. Brief introduction to VHDL structure Entity Architecture Structural/Data Flow/Behavioral descriptions What is it Syntax Special Cases File I/O

VHDL Presentation

E N D

Presentation Transcript

VLSI Design & Reconfigurable Computing ENG*6090(3)Advanced Topics in VHDLStephen CoeGuangfa LuFriday, March 07, 2003

VHDL Presentation • Brief introduction to VHDL structure • Entity • Architecture • Structural/Data Flow/Behavioral descriptions • What is it • Syntax • Special Cases • File I/O • Declaration • Open/Close • Textio • Test Benches • What are they • How to use • examples

VHDL Presentation • Aliases • What are aliases for? • Object Aliases • How to simplify complex data structure with aliases. • Signature • Non-object Aliases • Subprograms • Similar idea to other programming language • Parameter modes • Functions • Procedures • Generics and Configurations • Motivation • How to use them

VHDL • “VHDL” is a acronym which stands for VHSIC Hardware Description Language • “VHSIC” stands for Very High Speed Integrated Circuits • The purpose of this programming language is to assist circuit designers to describe the characteristics of circuit.

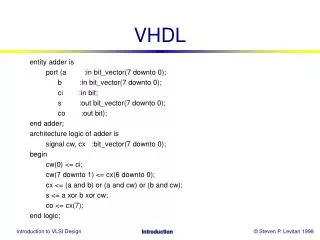

How VHDL Looks • Each section of VHDL code is broken down into two parts • The entity • which describes the interface and how the component or circuit interacts with the outside world • The architecture • which describes the function of the component or circuit

Name of Entity Name of Input Pins s q Latch r nq Name of Output pins The Entity The entity syntax entity latch is port (s,r: in bit; q, nq: out bit); end latch;

Description of the architecture (what it is) Description of circuit The Architecture The architecture syntax Entity name architecture belongs to architecture structure of latch is begin q<= r nor nq; nq<= s nor q; end structure; r q nq s

Description types • VHDL can be structured in three different ways. • Structural • Data flow • Behavioral • Usually, a mixture of all three methods are used in the design of the circuit

Structural Description • Structural description uses text to show how components of a circuit are put together • similar to a schematic capture approach to designing a circuit • It is to combine smaller blocks or predefined components into a larger circuit by describing the way that the blocks interact • The structural method is similar to a block diagram • smaller components are used to make a circuit without knowing what is happening in the block • It can be thought of as a netlist • A netlist is used to describes how components are connected together form a circuit

Component Pin Specifications } These are used to describe the input and output pins of the component nor_gate that will be used in the architecture section Structural Syntax Architecture description describes the architecture is of the method structure description and belongs to the entity latch entity latch is port (s,r: in bit; q, nq: out bit); end latch; architecture structure of latch is component nor_gate port (a,b: in bit; c: out bit); end component; begin n1: nor_gate port map (r, nq, q); n2: nor_gate port map (s=>a, q=>b, nq=>c); end structure; Mapping pins to component } The command port map is used to show how the input and output pins are connected to the component nor_gate

Description Representation Architecture s q a nor_gate c b a nor_gate c b r nq Entity

link a a sum sum b b carry carry HalfAdder HalfAdder Internal Signals • It is also possible to use internal signals to the architecture • These are signals that are only used for connectivity within the architecture. • This would be used if two components inputs and outputs are connected together without being connected to any pin described in the entity • They are defined between the architecture line and the begin line A Sum architecture structure of full_adder is component halfadder port (a,b: in bit; carry, sum: out bit); end component; signal link : bit; begin . . . End structure; B Carry C Full Adder

Advantages of Structural description • Hierarchy • allows for the simplification of the design • Component Reusability • allows the re-use of specific components of the design (Latch, Flip-flops, half-adders, etc) • Design Independent • allows for replacing and testing components without redesigning the circuit

Data Flow • Data flow describes how the data flows through the circuit, from input to output • It uses built in functions to describe the flow of data • All commands in Data flow are concurrent (occur at the same time) • Data flow operates in discrete time, when changes occur on the input, it immediately affects the output of the circuit • This method is like the more traditional way of designing a circuit using gates • For some traditional hardware designers, it is easier to use the data flow method, since it deals with the traditional method of designing circuits.

r q nq s Data Flow Syntax Architecture description describes the architecture is of the method data flow description and belongs to the entity latch entity latch is port (s,r: in bit; q, nq: out bit); end latch; architecture dataflow of latch is begin q<= r nor nq; nq<= s nor q; end dataflow; Logical Data Assignment Shows that the value of the output pins are derived from a logical function of the input pins } “<=” is used for a signal assignment, which describes how the data on the right hand side of the operator to the left hand side.

Behavioral Descriptions • Unlike the other two methods for describing the architecture, behavioral description is like a black box approach to modeling a circuit • It is designed to do a specific task, how it does it is irrelevant • It is used to model complex components which are hard to model using basic design elements • Behavioral is often more powerful and allows for easy implementation of the design • Most texts they combine both data flow and behavioral descriptions into one

Behavioral description • Behavioral descriptions are supported inside a process statement • A process is used to describe complex behaviors of the circuit • The contents of a process can include sequential statements • These sequential statements are similar to commands in conventional programming languages (it, for, etc) which can only be used in the body of a process statement • Although, inside a process is sequential, the process itself is concurrent, all processes in a architecture begin execution at the same time • The process statement is declared in the body of the architecture in the same way as signal assignments in data flow

Elements of a Process • Processes can have a list of signals that they depend on, a sensitivity list, or they can use wait signals to make the process wait for a event to occur (not both) • They are only execute if the signals in the sensitivity list change • This makes it critical to ensure that the signals that the process depends on are in the sensitivity list • Each process is executed once upon power up of the system • Wait statements are similar to sensitivity lists, but have the advantage of forcing a process to wait at any point within the process, not just the beginning.

Process syntax of a counter Process label (optional) Process is dependent only on variable “x” count: process (x) variable cnt : integer := -1; begin cnt:=cnt + 1; end process Variable is set to a value of -1 since the process is run once at startup to bring the value to 0 Increments the variable “cnt” every time the signal of “x” changes

Variables • Variables in VHDL behave similar to those in conventional programming languages • They are used to represent the state of a process and are local to that process • They are declared in a similar way to that of a signal in data flow or structural descriptions variable TempVar : integer := -1; • As shown above, Variables are declared before the begin keyword of a process

Variables and signals signal x, y, z : bit; process (y) begin x<=y; z<=not x; end process process (y) variable x,z : bit; begin x:= y; z:= not x; end process; • It should be realized that signals and variables are different. On the left both commands in the process are concurrent, they occur at the same time. This results in z not being the opposite of y but the opposite value of x when the process is begun • Since the example on the right is using variable, which are sequential, the value of z is the complement of y. • Signal assignment statements do not take effect immediately • Variable assignments take effect immediately

Behavioral vs. Structural vs. Data flow Structural How components are put together nor nor Data Flow Describes how data flows from input to output Behavioral Describes the behavior of the circuit within a process process (r,s) begin if (r nor nq) then q <= ‘1’; else q <= ‘0’; endif . . . end process

Files and Input/Output • A method of viewing and storing the results produced by simulation • They are used for long term data storage beyond just one simulation run • Saving result data to be analyzed in other programs • Assists in error checking your circuit • File handling can only be done during simulation of a circuit. • In VHDL, a file can only contain one type of object (bit, integer, bit_vector, text, etc) • The concept behind file handling in VHDL is similar to that of conventional programming languages except that you must declare a file object type. • Declaring a file pointer of specified object type • Opening the file • Reading/Writing data

Definition of File Type • The first step is to define the type of file in use, the type of information stored in that file type. • type file_type is file of element_type; • type IntegerFileType is file of integer; which defines IntegerFileType as a type that can only contain integer values • Once you have defined the type of file in use, the next step is the file declaration. • A file declaration creates one or more file objects (pointers) of a given file type. • File declarations occur between the process statement and the begin statement (similar to variables) • There are different declarations depending on the version of VHDL being used.

File Declaration • The syntax for VHDL-93 is followed: file identifier (,…) : subtype_indication [openfile_open_kindis “filename” ]; file_open_kind: read_mode write_mode append_mode Example: file infile: IntegerFileType open read_mode is “inputdata.txt” file outfile: IntegerFileType open write_mode is “outputdata.txt”; • The syntax for VHDL-87 is followed: file identifier : subtype_indication is [in | out] string_expression ; Example: file infile: IntegerFileType is in “inputdata.txt”; file outfile: IntegerFileType is out “outputdata.txt”;

file_open / file_close • Another way of opening files in VHDL-93 is similar to the conventional C programming language • the object of the file is created but the file is opened and closed within the body of the code • file_open and file_close commands are used to open and close the files. FILE identifier : file_type; PROCEDURE FILE_OPEN(FILE identifier:file_type; file_name: IN STRING; open_kind: FILE_OPEN_KIND := READ_MODE); PROCEDURE FILE_OPEN(status: OUT FILE_OPEN_STATUS; FILE identifier: file_type; file_name: IN STRING; open_kind: FILE_OPEN_KIND := READ_MODE); PROCEDURE FILE_CLOSE(FILE identifier: file_type);

Advantage of file_open/file_close • Determine how to open the file within program (read, write, append) • Can determine the name of the file you wish to open during the program (ie. User type in keyboard) • Allows the system to ensure the file is opened properly • file_open_status is used to verify the open operation is successfully. • Problems can occur if the file is declared in a component that is used multiple times. • Each instant of the component will attempt to open the same file

File Reading and Writing • In the basic reading and writing, the data stored and retrieved must be of the same type as the file declaration • In order to read from a file, the file must be opened in read_mode. • In writing information to a file, the file must be opened in either write_mode or append_mode. • This method of reading and writing is not very popular since it is bad for portability between operating systems and simulators. PROCEDURE READ(FILE identifier : file_type; value : OUT type_mark); PROCEDURE WRITE(FILE identifier : file_type; value : IN type_mark); FUNCTION ENDFILE(FILE identifier : file_type) RETURN BOOLEAN;

Textio Package • Textio is a standardized library for VHDL that allows data to be stored to a monitor or to a file in ASCII format • The standard library must be included at the top of the code use std.textio.all; • This increases the portability the data that is being stored so that it may be used on other simulators or platforms • It allows external software to read results for analyzing (spreadsheet, human eye, etc). • When defining a file for reading and writing using the Textio functions, the file declaration is of file type text • It is based on the concept of dynamic strings, accessed using pointers of type line • Textio uses the same idea as normal read/write to write the line of text to a file, but uses a command called writeline. • The difference is when creating the string of text, it converts all data to text

Writing information using Textio • In order to write information using Textio, the information must be formatted in a variable • Because of the variables, this operation must occur in a process • A write function converts the data to text and appends it to the end of the variable • This data can be bit, bit_vector, time, integer, real, boolean, character and string • Writeline is used to write the information in the variable to the file, then resetting the variable to null.

Example of Writing to file use textio.all; architecture behavior of check is begin process (x) variable s : line variable cnt : integer := 0; file output : TEXT isout “data.txt"; begin if (x = ‘1’ and x’last_value = ‘0’) then cnt:=cnt+1; if (cnt>MAX_COUNT) then write (s, ”Overflow – “); write (s, cnt); writeline (output, s); end if; end if; end process; end behavior Declaration of variables } This code writes to a file (assuming MAX_COUNT is 15): “Overflow – 15” } O v e r f l o w - 1 5 NULL Pointer ‘s’

Reading information using Textio • The reading of data is similar to the writing of data • The readline reads a complete line of data from the file and places it in a pointer of type line • The read function extracts characters from the beginning of the line and converts them into the expected type • In reading a string or a bit_vector of a certain length, it converts as much information as will fit into the variable • There is a optional parameter in the read command called good • Good is a Boolean value that returns if the read is successful or unsccessful depending on if there is a problem reading the data

Textio Input Example procedure read_v1d(variable v:out std_logic_vector) is variable buf : line; variable c : character ; file out_file : TEXT isin “data.txt"; begin readline (f , buf ); --read a line from the file. for i in v ’range loop read( buf , c ) ; --read a character from the line. case c is when ‘X’ => v (i) := ‘X’ ; when ‘U’ => v (i) := ‘U’ ; when ‘Z’ => v (i) := ‘Z’ ; when ‘0’ => v (i) := ‘0’ ; when ‘1’ => v (i) := ‘1’ ; when ‘-’ => v (i) := ‘-’ ; when ‘W’ => v (i) := ‘W’ ; when ‘L’ => v (i) := ‘L’ ; when ‘H’ => v (i) := ‘H’ ; when others => v (i) := ‘0 ’; end case; end loop; end; This is a procedure that is called to read in specific characters from a file, and place them into a vector The Vector for data to be stored were passed down as arguments of the procedure It should be noted that the file is opened in a procedure. This makes the file local to this procedure and is closed when procedure is finished

File Declared in subprograms • If a file object is declared in an architecture or a process, the files are opened at the start of the simulation and automatically closed again at the end of the simulation. • Opening files in a subprogram are local to only that subprogram and are automatically closed once the subprogram returns • Each time the procedure is called, a new physical file is created. • Example procedure write_to_file is file FilePtr : data_file_type open write_mode is “datafile”; begin … end procedure write_to_file;

VHDL Test Bench • VHDL test bench is VHDL code that produces stimuli to test your design correctness • It can automatically verify accuracy of the VHDL code • Given a known input, does the system generate the expected output • Verifies that the VHDL code meets the circuits specifications • Test benches should be easily modified, allowing for future use with other code • Should be Easy to understand the behavior of the test bench

Purpose for Test Bench • To generate stimulus signals for simulation • Generate specific stimuli based on the previous output response • Apply a basic waveform with discrete time intervals • Import test data from files b) To apply these stimulus to the VHDL code under test and collect the actual output responses c) To compare the output responses with the values expected

Stimulus Generation/Response • There is three general ways of generating a simulation for testing • Repetitive patterns • Patterns can generated using different frequencies and periods • Combination of waveforms • (Waveform A and B) • Lookup table • Constant table • I/O data • Keyboard • Data file • Response Handling • The response from the system can be dumped to a file to be analyzed by a external program or human eye (Textio). • Analyzed by test bench to verify expected output.

Test Bench Unit Under Test Monitor Program that generates output Resulting Output File Program that generates Stimuli Human Eye or External Program

Full Adder Sample Test Bench with output --Clock for BCLOCK2: processbegin b <= '0'; wait for CLK_PERIOD; b <= '1'; wait for CLK_PERIOD;end process;--Clock for CCLOCK3: processbegin c <= '0'; wait for CLK_PERIOD*2; c <= '1'; wait for CLK_PERIOD*2;end process; MONITOR: process variable output_line : line; file out_file : TEXT isout "results.txt"; Begin write (output_line ,a); write (output_line, b); write (output_line, c); write (output_line, sum); write (output_line, carry); writeline (out_file, output_line); wait a,b,c,sum,carry; end process; END testbench_arch; ARCHITECTURE testbench_arch OF testbench IS COMPONENT full_adder PORT (a, b, c : in std_logic;sum, carry : out std_logic); END COMPONENT; SIGNAL a , b, c, sum, carry : std_logic; --Defining the variable "CLK_PERIOD" --to be equal to 20 nano seconds constant CLK_PERIOD : time:= 20 ns; BEGIN--Defining external interface signals --to Unit Under Test. UUT : full_adder PORT MAP ( a => a, b => b, c => c, sum => sum, carry => carry); CLOCK: process begin a <= '0'; wait for CLK_PERIOD/2; a <= '1'; wait for CLK_PERIOD/2; end process;

Full Adder Sample Test Bench with output 2 MONITOR: process variable output_line : line; file out_file : TEXT isout "results.txt"; Begin write (output_line ,a); write (output_line, b); write (output_line, c); write (output_line, sum); write (output_line, carry); writeline (out_file, output_line); wait a,b,c,sum,carry; end process; END testbench_arch; ARCHITECTURE testbench_arch OF testbench IS COMPONENT full_adder PORT (a, b, c : in std_logic;sum, carry : out std_logic); END COMPONENT; SIGNAL a , b, c, sum, carry : std_logic; --Defining the variable "CLK_PERIOD" --to be equal to 20 nano seconds constant CLK_PERIOD : time:= 20 ns; BEGIN--Defining external interface signals --to Unit Under Test. UUT : full_adder PORT MAP ( a => a, b => b, c => c, sum => sum, carry => carry); READDATA: process file out_file : TEXT isin “data.txt"; variable buf : line; variable A,B,C : std_logic ; begin readline (f , buf ); --read a line from the file. read( buf , A ) ; --read a character from the line. read( buf , B ) ; read( buf , C ) ; a<=A; b<=B; c<=C; wait for CLK_PERIOD; end process