8224 words x 14 bits Memory Example with Row and Column Redundancy

80 likes | 335 Views

8224 words x 14 bits Memory Example with Row and Column Redundancy. Gary Waggoner February 24, 2008. Memory Architecture 8224 words, 14 bits, mux 16. Rows 512 and 513. 2 Spare rows (Top Bank). 2 Spare rows (Bottom Bank). Rows 0 thru 511. Bit 0. Bit 6. Bit 7. Bit 14.

8224 words x 14 bits Memory Example with Row and Column Redundancy

E N D

Presentation Transcript

8224 words x 14 bits Memory Example with Row and Column Redundancy Gary Waggoner February 24, 2008

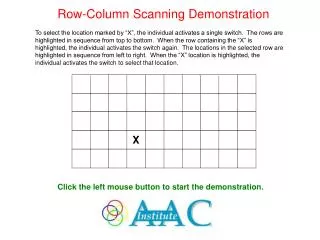

Memory Architecture8224 words, 14 bits, mux 16 Rows 512 and 513 2 Spare rows (Top Bank) 2 Spare rows (Bottom Bank) Rows 0 thru 511 Bit 0 Bit 6 Bit 7 Bit 14 1 group of 8 spare columns (left half) 1 group of 8 spare columns (right half)

Spare Elements • Any spare row in bottom bank can repair any row in the bottom bank • Any spare row in the top bank can repair either of the rows (only 2) in the top bank • Any group of 8 columns in left array can be repaired • Any group of 8 columns in the right array can be repaired

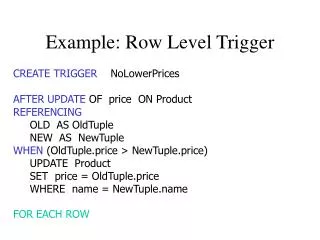

CTL (using Slimane’s proposal) Signals { “Q”[13..0] Out; “A”[13..0] In; “D”[13..0] In; “CRE1” In; “FBA1” [3..0] In “CRE2” In; “FBA2” [3..0] In “RRE1” In “FRA1”[8..0] In “RRE2” In “FRA2”[8..0] In “RRE3” In “FRA3” In “RRE4” In “FRA4” In }

CTL (continued) Environment “myStrangeMemory” { CTL { CRE1 { DataType RepairEnable {ActiveState ForceUp;}} FBA1[3] { DataType RepairAddress;} FBA1[2..0] {DataType RepairDataBit;} CRE2 { DataType RepairEnable {ActiveState ForceUp;}} FBA2[3] { DataType RepairAddress;} FBA2[2..0] {DataType RepairDataBit;} RRE1 {DataType RepairEnable {ActiveState ForceUp;}} FRA1[8..0] {DataType RepairAddress;} RRE2 {DataType RepairEnable {ActiveState ForceUp;}} FRA2[8..0] {DataType RepairAddress;} RRE3 {DataType RepairEnable {ActiveState ForceUp;}} FRA3 {DataType RepairAddress;} RRE4 {DataType RepairEnable {ActiveState ForceUp;}} FRA4 {DataType RepairAddress;} }

CTL (continued) MemoryProperties { SimultaneousReadWrite None: ColumnMultiplexing 16: TopologicalOrg Adjacent; } MemoryRepair{ RepairResource Column1 { RepairType Column; AccessSignals ‘CRE1 + FBA1[3..0]’ Width 4 AddressMap xxxxxxxxxxrxxx DataBitMap 0rrr /* this doesn’t work because Column1 cannot repair bit 7 */ } RepairResource Column2 { RepairType Column; AccessSignals ‘CRE2 + FBA2[3..0]’ Width 4 AddressMap xxxxxxxxxxrxxx DataBitMap 1rrr }

CTL (continued) RepairResource Row1 { RepairType Row; AccessSignals ‘RRE1 + FRA1[8..0]’ AddressMap 0rrrrrrrrrxxxx } RepairResource Row2 { RepairType Row; AccessSignals ‘RRE2 + FRA2[8..0]’ AddressMap 0rrrrrrrrrxxxx } RepairResource Row3 { RepairType Row; AccessSignals ‘RRE3 + FRA3’ AddressMap 1xxxxxxxxrxxxx } RepairResource Row4 { RepairType Row; AccessSignals ‘RRE4 + FRA4’ AddressMap 1xxxxxxxxrxxxx } }

Conclusion • Address and Data maps don’t work when there is a non power of 2 split in the address or data space • Otherwise, the format works well.