South Bridge

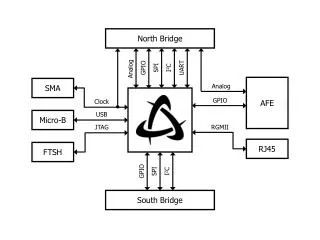

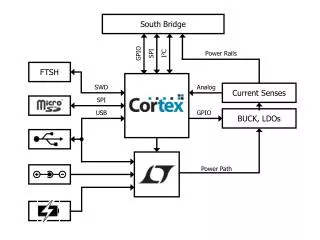

North Bridge. GPIO. SPI. I 2 C. UART. Analog. AFE. SMA. Analog. GPIO. Clock. USB. Micro-B. RGMII. JTAG. RJ45. FTSH. I 2 C. GPIO. SPI. South Bridge. North Bridge. AFE. VSUP - 3.6V ~ 5V. D3V3 - Digital 3.3V. D1V5 - Digital 1.5V. A1V5 - Analog 1.5V. A3V3 – Analog 3.3V.

South Bridge

E N D

Presentation Transcript

North Bridge GPIO SPI I2C UART Analog AFE SMA Analog GPIO Clock USB Micro-B RGMII JTAG RJ45 FTSH I2C GPIO SPI South Bridge

North Bridge AFE VSUP - 3.6V ~ 5V D3V3 - Digital 3.3V D1V5 - Digital 1.5V A1V5 - Analog 1.5V A3V3 – Analog 3.3V ETH PHY South Bridge

SmartFusion MSS CCC FPGA fabric EXT CLK OUT EXT CLK IN GLC 20 MHz to SMA 20 MHzfrom SMA PLL REF CLK OUT GLB MAIN CLK IN 20 MHzfrom TCXO 20 MHz (differential) to mezzanine GLA0 AFE 1 CLK AFE 2 CLK max. 20 MHz to AFEs (DDR) CLKC MSS 32 kHzOSC CCC USB CLK LP XTAL 32 kHzfrom XTAL 60 MHz from USB chip RMII CLK 50 MHz from ETH OSC

North Bridge ADC, DAC VSUP D3V3 D1V5 ETH PHY A1V5 A3V3 South Bridge

North Bridge Analog GPIO SPI I2C LED Jack/BNC Analog GPIO Clock I/O SMA SRAM EMI JTAG FTSH I2C JTAG GPIO SPI South Bridge

SmartFusion MSS CCC FPGA fabric EXT CLK IN EXT CLK OUT GLC PLL REF CLK OUT GLB MAIN CLK IN AFE1 CLK GLA0 AFE2 CLK CLKC MSS 32 kHzOSC CCC USB CLK LP XTAL RMII CLK ETH PHY

SmartFusion Fabric MSS CCC CCC EXT CLK IN GLC REF CLK OUT PLL EXT CLK OUT GLB MAIN CLK IN CCC CCC USB CLK AFE1 CLK CLKC GLA0 AFE2 CLK 32 kHzOSC CCC MSS CCC LP XTAL RMII CLK ETH PHY

SmartFusion FPGA Fabric CCC CCC REF CLK OUT DUT MSS CCC EXT CLK IN GLC EXT CLK OUT PLL GLB MAIN CLK IN CCC USB CLK AFE1 CLK AFE2 CLK CLKC GLA0 32 kHzOSC MSS CCC CCC LP XTAL RMII CLK ETH PHY

32 kHzOSC FPGA Fabric CCC CCC LP XTAL REF CLK OUT DUT MSS CCC EXT CLK OUT PLL MAIN CLK IN CCC GLB USB CLK GLC EXT CLK IN AFE1 CLK AFE2 CLK RMII CLK GLA0 ETH PHY MSS CCC CCC

32 kHzOSC FPGA Fabric CCC CCC LP XTAL REF CLK OUT DUT MSS CCC EXT CLK OUT PLL MAIN CLK IN CCC GLB USB CLK GLC EXT CLK IN AFE1 CLK AFE2 CLK RMII CLK GLA0 ETH PHY MSS CCC CCC

MSS CCC CCC REF CLK OUT MAIN CLK IN MSS CCC EXT CLK OUT EXT CLK IN CCC USB CLK LP XTAL AFE1 CLK ETH CLK AFE2 CLK ETH PHY CCC CCC

CCC CCC REF CLK OUT MAIN CLK IN EXT CLK IN EXT CLK OUT CCC LP XTAL USB CLK ETH CLK CCC CCC