第三章 组合逻辑电路设计

250 likes | 402 Views

第三章 组合逻辑电路设计. 组合逻辑电路: 输出仅和当前的输入有关。. §3-1 集成逻辑电路的电气特性 §3-2 常用组合逻辑模块 §3-3 组合电路的设计方法 §3-4 险象与竞争 §3-5 小结. §3-3 组合电路的设计方法. 设计: 已知功能要求,导出逻辑电路。. §3-3-1 简单组合逻辑设计 §3-3-2 功能分析和函数分解 §3-3-3 改进原电路,实现新功能 §3-3-4 积木块化设计. §3-3-1 简单组合逻辑设计. 将待设计电路视为一不可分割的整体,用一个真值表或一组逻辑

第三章 组合逻辑电路设计

E N D

Presentation Transcript

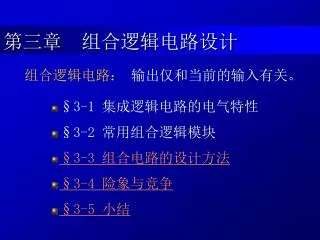

第三章 组合逻辑电路设计 组合逻辑电路: 输出仅和当前的输入有关。 • §3-1 集成逻辑电路的电气特性 • §3-2 常用组合逻辑模块 • §3-3 组合电路的设计方法 • §3-4 险象与竞争 • §3-5 小结

§3-3 组合电路的设计方法 设计:已知功能要求,导出逻辑电路。 • §3-3-1 简单组合逻辑设计 • §3-3-2 功能分析和函数分解 • §3-3-3 改进原电路,实现新功能 • §3-3-4 积木块化设计

§3-3-1 简单组合逻辑设计 将待设计电路视为一不可分割的整体,用一个真值表或一组逻辑 方程来描述电路的逻辑功能,是最基本、最易掌握的方法。

简单组合逻辑设计(续) AB 00 01 11 10 A 0 1 S1S0 S1S0 00 0 0 1 1 00 0 1 01 1 1 0 0 01 1 0 11 1 0 1 0 11 B 10 0 1 0 1 10 B

3.3.2 功能分析和函数分解 功能分析-分解为若干模块-构成逻辑框图; 设计各模块-完成整个电路的设计。自上而下的设计方法。 例1:用4位加法器构成补码变换器: 输入原码:S B3B2B1B0 输出补码:S F3F2F1F0 其中S为符号位。

例2:用4位加法器构成加/减运算电路: 输入无符号原码: [A]原=A3A2A1A0,[B]原=B3B2B1B0 M=0时,计算A+B(无溢出) M=1时,计算A-B 输出原码:S F3F2F1F0, 其中S为符号位。

设[A]原+[B]反=COX3X2X1X0 |A|>|B|时,CO=1,F3F2F1F0=X3X2X1X0 ,S=0 |A|≦|B|时,CO=0,F3F2F1F0= ,S=1 S=M·CO CI=M·CO

自上而下的设计方法:待设计的电路较复杂时,一次分解后得到自上而下的设计方法:待设计的电路较复杂时,一次分解后得到 的各 模块还需进一步分解,功能分析和 划分继续一层层地进行,直到所有的模块 均可用已有的标准模块或门电路来实现。 问题:A和B是两个4位无符号的二进制数,试设计一个大数 减小数电路,当A>B时,输出A-B,当A≤B时, 输出B-A。

§3-3-3 改进原电路,实现新功能 例1:用4位加法器构成余3码到8421码的转换器

§3-3-4 积木块化设计 x3 c3 x FA co HA y3 Σ3 y c2 Σ x2 FA 一位半加器 y2 Σ2 c1 xi co FA x1 yi FA y1 Σ cii Σ1 c0 x0 HA y0 Σ0 一位全加器 四位并行加法器 积木块化设计:用标准模块(积木块)来构成待设计 的电路。

§3-4 险象与竞争 静态输出(稳态输出):输出与输入的关系由电路的 真值表决定的。 • 险象(毛刺):电路产生瞬时的错误输出。 • 险象产生的条件: • 电路的各元件存在传输延迟时间; • 任何两个输入信号不可能同时发生变化; • 输入信号的上升时间和下降时间均不为0。

§3-4 险象与竞争 险象的极性为负:0型险象。

险象与竞争 §3-4-1 逻辑竞争与险象 §3-4-2 功能险象 §3-4-3 由tr和tf引起的险象 §3-4-4 动态险象 §3-4-5 险象的消除

§3-4-1 逻辑竞争与险象 逻辑竞争: 某一输入信号的变 化沿不同的路径到 达输出端的现象。 逻辑险象: 由逻辑竞争产生的 险象。 临界竞争: 产生险象的竞争。 非临界竞争:不产生险象的竞争。

某一输入变量在表达式中以原变量和反变量的形式同时出现,则该变量的变化将引起逻辑竞争,否则不会引起逻辑竞争。当表达式中其他变量取某种特定值,使表达式简化为 则X的变化将引起临界竞争。产生0型(1型)险象。 • A C F A B F • 0 0 B+B 0 0 C • 0 1 B 0 1 1 • 0 B 1 0 C • 1 1 B 1 1 C 逻辑险象的表达式判别 在A=C=0时,B的变化可能产生0型险象。

逻辑险象的卡诺图判别 如果在卡诺图中有两个相临的最小项分别被两个相切的卡诺圈包含而未被同一个卡诺圈包含,则输入信号在与这两个最小项对应的组合间变换时将出现临界竞争。最大项情况与此类似。要消除逻辑险象可增加冗余项。

《数字设计引论》§3-4险象与竞争 图3-4-5 电路测试

《数字设计引论》§3-4险象与竞争 图3-4-6 功能险象

§3-4-2 功能险象 功能险象: 两个或两个以上的输入信号逻辑上同时变化; 实际电路中,由于延时不同而不可能同时变化; 当变化前和变化后的输出相同时; 变化过程中可能产生功能险象。 011-111-110 1-1-1 011-010-110 1-0-1 000-100-101 0-1-0

§3-4-4 动态险象 当输入变化前后输出信号的稳定值不同,但输入的变化引起输出交替产生正向和负向的毛刺。 000-100-101-111 0-1-0-1

《数字设计引论》§3-4险象与竞争 图3-4-8 例3-4-3电路图及卡诺图

§3-4-5 险象的消除 加选通信号: 加滤波电容:

§3-4-6 小结 一、一般逻辑函数可用MUX或译码器实现。 MUX: 一片MUX实现单一逻辑函数,常 用卡洛图降维法。 译码器:译码器加与非门(对应最小项表达 式)、或门(对应最大项表达式)实现 多输出函数。 二、充分利用现有的功能模块实现组合逻辑 函数。