OCP Debug Socket for Multi-Core Debugging

ESC Apr 1, 2008 Mark Burton Bob Uvacek Neal Stollon. OCP Debug Socket for Multi-Core Debugging. Introduction. - What multicore debugging paradigms do we have today, what paradigms are coming, and what paradigms must we overcome? we have one core at a time with debuggers that are prepared

OCP Debug Socket for Multi-Core Debugging

E N D

Presentation Transcript

ESC Apr 1, 2008 Mark Burton Bob Uvacek Neal Stollon OCP Debug Socket for Multi-Core Debugging

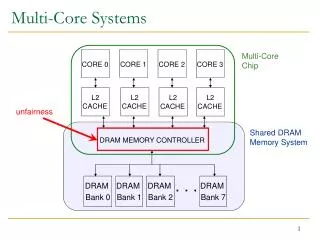

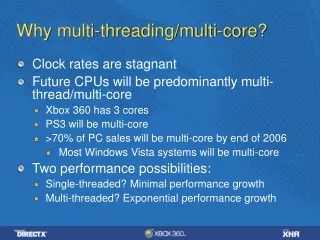

Introduction - What multicore debugging paradigms do we have today, what paradigms are coming, and what paradigms must we overcome? we have one core at a time with debuggers that are prepared we will have any 2 cores at a time in comparative debugging with debuggers that do not need adaptation we must overcome: Tell us when you need a second core and we will adapt our debugger within 6 months - What are the strengths and weaknesses of the current generation of tools? Limited since proprietary, not prepared for competition cores or Limited if public but not supported for 2 cores at the same time Good since very well adapted for one specific core with scripts for register names and internal memories address spaces - What new approaches and techniques will impact our ability to debug multicore software, and can we hope to see an impact as significant as that of source-level debugging when it was introduced decades ago? XML files for hardware topology and register address spaces will come out with every new chip Future has general debuggers that adjust operation based on XML and work for any 2 cores out of many at a time for comparative debugging - What is the role of standards in enabling a multicore debug ecosystem to grow and scale into the future? Standards enable preparation of tools in software and hardware before chips are built; big speed up in multi-core ASIC projects - What silicon features are not being fully exploited today, and what new features will be needed? Assertions in silicon and “slow” service buses and ETM like HW on chip was not fully deployed but will be in smaller geometries Asynchronous debug needs timer stamps everywhere and needs thread decoding made usually in processors to become accessible also for debug - How do you observe and control several different kinds of processors concurrently at a reasonable level of abstraction, and with a reasonable approximation to cycle-accuracy? There can by synchronized clock for debug only sessions ; There can be multi-core cross-trigger HW; there can be There can be at speed buffer recording with time stamps of several cores for 100 cycles and slow read-out over trace afterwards There can be transaction begin/end recording from multiple cores on many PtP buses like NoC and display on one time axis for comparison.

OCP Debug Socket for Multi-Core Debugging OCP-IP announces the release of its Debug Standard. The new standard identifies Basic and Extended sets of socket level signals for debugging of multiple processor cores connected with the OCP interface. The standard represents a breakthrough allowing designers to distribute debug signals as part of the system interface scheme; rather than wired separately from the data path as had been previously been the case. This innovative new approach greatly enhances system providers ability to prepare multi-core debug hardware and software.

Debug Environment 3rd party CPUDebugger Target Server(s) 3rd party DSPDebugger Standard Debug API (SPRINT) SoC (Model) CPU Target Description IP-XACT, XML HWIP DSP Different Debug IF

NEW OCP Debug Standard 3rd party CPUDebugger 3rd party DSPDebugger Connect one “service/debug channel” independent of applications to all MP hardware blocks. Include a “service class” in all new MP software that can access the service channel on chip. Tag the “Transactions” as smallest common element to observe, debug, trace, benchmark, … Basic OCP Debug Interface Standard Debug API (SPRINT) Extended OCP Debug Interfaces OCP Debug Compatible fabric B U S F A B R I C CPU Target Description IP-XACT, XML Access HW Debug HW HWIP Target Server DSP The SPRINT software standard is related to our work as a general debug functionality description for multiple processors.

OCP Debug Standard Advantages Simplifies debug - Standardized Basic OCP Debug Socket for all OCP IP - Several application specific options Debug Hardware and Software for multi-core debugging can be offered as standard IP Opens implementation and support of more (heterogeneous) processors inside one debug GUI Proprietary Debug solutions supported - Need just OCP Debug wrapper Fixed OCP debug interface, is still open to a multitude of debug interconnects (I.e. Nexus style, or serial buses, or cross bar, or NoC, etc) We expect high uptake of the new standard in the OCP-IP community (Reusable IP blocks)

Connection with SPRINT SPRINT’s functionality API is utilized for multiple core debugging. The SPRINT Debug API is related to the OCP-IP standard as a general debug functionality description for multiple processors. SPRINT’s Debug API defines all the transactions and formats that must be realized by the debug hardware and is supported by the OCP-IP standard. SPRINT is providing the definition of the debug functionality which we refer to in the OCP-IP Debug standard. The SPRINT Debug API is expected to be available on GreenSocs.com Q208.

Definition of Debug Hardware-IP Block and Environment SoC Debug Solutions Have 5 Hardware and 2 Software Interfaces • Debug-IP HW connections to SoC: • 1 CORE-INTERFACE: interfaces to core IP-block debug data/control proprietary IO • 2 BUS-INTERFACE: interface to a bus traffic [event/trace data collect, compression and triggering] • 3 CROSS-TRIGGER INTERFACE: to other debug-IP blocks [event-synch.] • 4 PIN-INTERFACE CONTROL: IF to JTAG for debug control to analyser/debugger software. • 5 PIN-INTERFACE DATA: interface for high speed data [like Nexus] • Debug software API for information transfer and display: • A. System Debug SW API interface • B. EDA API interface – block and system level • verification (ESL, RTL) CHIP Cross trigger IF 3 OCP Bus fabric Bus test socket 1 Core Debug IF Trace IF 2 Memory-mapped JTAG-mapped Nexus-mapped Debug-IP registers Debug IF 4 5 Nexus data-trace JTAG control Debug Software SYS API EDA API A B

Essential Debug Infrastructure • Standardized OCP Debug solution consists of: • Debug hardware for multi-core OCP Debug Sockets • Debug software for 2 or more cores in one GUI (following SPRINT recommendation) • XML file to expose debug topology and processor cores (following SPRINT rules) • XML file to define the OCP Debug Interface signals (following SPIRIT framework) • OCP interconnect generator to automate debug sockets wiring on a chip • The central OCP-IP Debug Standard mission is to define the first two. • The next three substantially increase comfort when working with debug solutions.

What is in the Debug Specification? OCP Interface for Basic Debug Signals • Debug Control and Run Control for Cores • Consistent (multiple) processor software debugger interfaces • Cross-Triggering between Multiple Cores and Events • Scalable to on-chip/off-chip cross triggering • Trace Interface • Bus traffic observation (system trace) and control (triggering) • New classes of debug errors (different from system errors) OCP Interface for Extended Signals (Special features) • Performance Monitor • Time-stamping • Power Monitoring voltage islands, gated clock islands • Security islands Of huge valuein final silicon

OCP Debug Interface Signals, BASIC Cross-Triggering Socket Cross-Control Socket Reset Socket ReqDebug Msuspend DebugSerror DebugCon NoSResp ForceResp ForceAbort ForceAbortAck Trigger_in_condition[n:0] Trigger_out_action[n:0] Trigger_out_enable[n:0] Ext_trig_clk Ext_condition[n:0] Ext_action[n:0] Debug_rest_n Debug_en JTAG Socket Tck Trst Tms Tdi Tdo Run Control Socket Trace Socket SyncRun SyncRunAck TraceTrigger[x]

OCP Debug Interface Signals, EXTENDED Power-down Monitoring Socket Performance Monitoring Socket MConnID MchannelID MreqWatch[x] PMSampling Srbbesp[2:0] PWRDomainStatus CLKDomainStatus Security Socket Timestamp Socket MreqSecure DebugMode[1:0] TraceMode[1:0] TAPenable Ts_clk Ts_reset

Summary Main philosophy is: Debug N cores on a chip by selecting any 2 or more cores for a time-aligned comparative debug session. • OCP-IP has standardized the Debug Interface between system bus and any/multiple processor cores and IP-blocks in a SoC design. • Enables reusable multi-core Debug-Hardware solutions. (OCP/JTAG/Nexus/MIPI) • Enables Debug-Software for multiple cores in one GUI. (See SPRINT debug APIs) • This will open the market for SoC designers to buy verified multi-core debug-IP solutions. (See IP-Extreme, HDL-Dynamics, Temento, ... IP providers)

OCP Debug Information • OCP public white papers are at: www.ocpip.org/socket/whitepapers/ • OCP members get the standard at: www.ocpip.org/members/ocpspec/ • OCP membership admin: admin@ocpip.org • Non-members can access this standard using an on-line, click-through research License