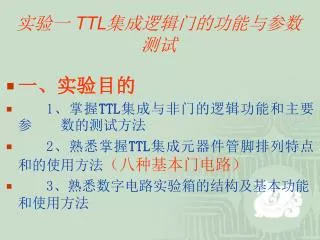

实验一 TTL 集成逻辑门的功能与参数测试

实验一 TTL 集成逻辑门的功能与参数测试. 一、实验目的 1、掌握 TTL 集成与非门的逻辑功能和主要参 数的测试方法 2、熟悉掌握 TTL 集成元器件管脚排列特点和的使用方法 (八种基本门电路) 3、熟悉数字电路实验箱的结构及基本功能和使用方法. V CC

实验一 TTL 集成逻辑门的功能与参数测试

E N D

Presentation Transcript

实验一 TTL集成逻辑门的功能与参数测试 • 一、实验目的 • 1、掌握TTL集成与非门的逻辑功能和主要参 数的测试方法 • 2、熟悉掌握TTL集成元器件管脚排列特点和的使用方法(八种基本门电路) • 3、熟悉数字电路实验箱的结构及基本功能和使用方法

VCC GND & & • 二、实验原理 • TTL集成与非门 是数字电路广泛使用的一种基本逻辑门,使用时必须对它的逻辑功能、主要参数和特性曲线进行测试,以确定其性能好坏。而本实验采用四输入双与非门74LS20,即在一块集成块内含有两个互相独立的与非门,每个与非门有四个输入端。其逻辑框图、符号及引脚排列如图1-1 • 14 13 12 11 10 9 8 • 1 2 3 4 5 6 7 • 图1-1 74LS20逻辑框图、逻辑符号及引脚排列 • :

VCC GND & & & • 1、与非门的逻辑功能 • 与非门的逻辑功能为:当输入端中有一个或一个以上是低电平时,输出 • 端为高电平;只有当输入端全部为高电平时,输出端才是低电平。 • 逻辑表达式为: Y=ABCD • 2.与非门的逻辑功能测试 • 1)逻辑电路及74LS20芯片逻辑功能测试的连接方法如图1-3所示。 • 14 13 12 11 10 9 8 • 图1-2逻辑电路 1 2 3 4 5 6 7 • A B C D接发光二极管 • 输入接逻辑开关 H L H L H L H L • 图1-3 74LS20芯片引脚连接图 • 注意:“H”表示高电平 “1”;“L”表示低电平 “0”。

mA & • 三、实验任务 • TTL与非门的主要参数 • (1)低电平输出电源(空载导通)电流ICCL和高电平输出电源(空载截止)电流ICCH 。 • 与非门处于不同的工作状态,电源提供的电流是不同的。 ICCL是指所有输入端悬空,输出端空载时,电源提供器件的电流。ICCH是指输出端空截,每个门各有一个以上的输入端接地,其余输入端悬空,电源提供给器件的电流。通常ICCL> ICCH它们的大小标志着器件静态功耗的大小。器件的最大功耗为PCCL=VCCICCL,手册中提供的电源电流和功耗值是指整个器件总的电源电流和总的功耗。 ICCL和ICCH 测试电路如图1-4(a)、(b)所示。 • 注意: TTL电路对电源电压要求较严,电源电压VCC只允许在+5V±10%的范围内工作,超过5.5V将损坏器件;低于4.5V器件的逻辑功能将不正常。 VCC +5V ICCL • TTL与非门静态参数测试电路

(2)低电平输入电流(输入短路电流)IIL和高电平输入电流(交叉漏电流)IIH。 *(3)输入开门电平VON和关门电平VOFF VON和VOFF 两个数值越靠近,越接近同一数值(阈值电平Vr)就说明与非门电路的特性曲线转换愈陡,抗干扰能力越强。 *(4)输出高电平VOH和输出低电平VOL (5)扇出系数NO (图1-6 ) 扇出系数是指门电路能驱动同类门的个数,它是衡量门电路负载能力的一个参数,TTL与非门有两种不同性质的负载,即灌电流负载和拉电流负载,因此,有两种扇出系数,即低电平扇出系数 NOL和高电平扇出系数 NOH。通常。 IIH<IIL,则 NOH>NOL,故常以 NOL作为门的扇出系数。 NOL= IOLmax/ IIL NOL≥8 (6)电压传输特性(图1-7 ) 门的输出电压VO随输入电压Vi而变化的曲线VO=f(Vi)称为门的电压传输特性,通过它可测试门电路的一些重要参数,如输出高电平 VOH;输出低电平 VOL、关门电平Voff、开门电平VON、阈值电平Vr、抗干扰容限VNL、VNH等(低电平噪声容限VNL= VOFF -VOL;高电平噪声容限VNH= VOH-VON)。 测试电路如图1-7所示,采用逐点测试法,即调节RW,逐点测得Vi及VO然后绘成曲线。

四、实验要求 • 1、查阅附录2,熟悉所用器件引脚排列图。 • 2、根据实验表1.1 74LS20四输入双与非门主要参数,画出它们 的测试逻辑电路图。 • 五、实验报告 • 1、对主要参数进行实验测试,记录测试结果同表1.1对照。 • 2、总结TTL门主要参数电路测试方法。

& & & & =1 门电路: A A B C Y B D Y E C D F E F 要求写出真值表,表达式并测试 =1

实验二 组合电路逻辑设计 • 一、实验目的 • 1、熟悉基本门电路功能及测试方法 • 2、掌握组合逻辑设计方法 • 3、对数电实验箱的使用 • 二、设计原理 • 组合逻辑电路是最常见的逻辑电路,其特点是在任何时刻电路的输出信号仅取决于该时刻的输入信号,而与信号作用前电路原来所处的

状态无关。组合逻辑设计,按照具体逻辑问题设状态无关。组合逻辑设计,按照具体逻辑问题设 • 计出最简单的逻辑电路。使用小规模集成电路(SSI)进行组合逻辑设计的一般过程是: • 1 、根据设计任务要求进行逻辑抽象,确定输入与输出变量; • 2 、列出真值表,并写出输出逻辑函数表达式; • 3 、通过卡诺图化简法求出化简的逻辑表达式,并按照已有的逻辑门的类型变换逻辑表达式。在由化简(变换)后的逻辑表达式,画出逻辑图,用标准器件连接逻辑电路。对其进行验证正确性。

三 、设计任务 • 1 、用2输入异或门和与非门设计一个路灯控制电路。已知总电源开关和三个路灯开关而三个开关能独立的控制路灯的亮灭。 • .写出输入输出变量; • .列出真值表,通过卡诺图化简法化简逻辑表达式,并按照已给的逻辑门的类型变换逻辑表达式。 • .通过变换的逻辑表达式,画出逻辑图。 • .验证其正确性。

2 、用与非门设计一个十字路口交通信号灯控制电路。 • 同上的设计思路。 • 四 、按指导书的要求完成实验及报告

& & & & =1 14 14 14 13 13 13 12 12 12 11 11 11 10 10 10 9 9 9 8 8 8 74LS20 74LS86 74LS00 1 1 1 2 2 2 3 3 3 4 4 4 5 5 5 6 6 6 7 7 7 =1 • 图 • Y=A·B·C·D Y=A·B Y=A⊕B • vcc 4B 4A 4Y 3B 3A 3Y vcc 2D 2C NC 2B 2A 2Y 1A 1B 1Y 2B 2A 2Y GND 1A 1B NC 1C 1D 1Y GND vcc 4B 4A 4Y 3B 3A 3Y 1A 1B 1Y 2B 2A 2Y GND

=1 =1 & & 实验内容1.路灯控制电路设计: 1、真值表: 2、表达式 • Y=(ABC+ABC+ABC+ABC)Z • =((AB+AB)C+(ABC+ABC))Z • =((A⊕B)C+(AB⊕AB)C)Z • =(A⊕B⊕C)Z • 3、电路图: • A 1 • B 23 4 • C 5 61 3 45 6Y • Z 2

& & & & & & & & 实验内容2:交通灯控制器电路设计南北方向为主通道 A;东西方向为次通道 B; 2、表达式:出现特殊情况时E(如警车); • 1、真值表: F1 = ABE=ABE • F2 = ABE = ABE • 3、电路图: • A • F1 • B • E • F2

& & & & & & & & 实验内容3. 4位数字代码锁设计代码为:ABCD=1010开锁信号:E=1、E=0闭锁;开锁式:Z=A B C D E 1.当代码错,E为1时报警; 2.当E=0,时无论代码为多少都不开门也不报警; 3.用与非门74LS0O,74LS20; 4. 根据给定芯片化简及变换逻辑表达式: • Y =ABCDE = ABCD+E = AC+B D E • = AC B D E • A • C • B • D Y • E

四、实验要求 • 1、查阅附录2,熟悉所用器件引脚排列图。 • 2、根据实验任务要求写出设计步骤,画出逻辑电路图。 • 五、实验报告 • 1、写出实验任务的设计过程,画出设计的电路图。 • 2、对所设计的电路进行实验测试,记录测试结果。 • 3、总结组合电路设计体会。 • 六、预习 • 1.数据选择器74LS153、译码器74LS138逻辑功能并测试。 • 2.内容见指导书

数电实验箱插座平面图 数码管 数 码 管 译 码 驱 动 16 — 1 14 —1 14 — 2 DIP -20 DIP -18 16 — 2 74LS192 14 —3 74LS86 14 — 4 74LS20 DIP16 74LS138 14 — 6 16 — 4 14 —5 74LS00 16 — 6 74LS138 16--7 74LS153 8-3 16 — 4 16 —5 14 —7

实验三 中规模组合逻辑设计 • 一、实验目的 • 1、掌握中规模集成芯片数据选择器和译码器的逻辑功能和使用方法 • 2、熟悉组合功能器件的应用 • 二、实验原理 • 1、数据选择器 • 数据选择器又叫多路选择器或多路开关,它是多输入,单输出的组合逻辑电路。由地址码控制器多个数据通道。实现单个通道数据输出,还可以实现数据传输与并串转换等多种功能。 • 它基本是由三部分组成:数据选择控制(或称地址输入)、数据输入电路和数据输出电路,它的种类多样有原码形式输出、反码形式输出,现以74LS153为例进行应用设计。

VCC 2S A0 2D3 2D2 2D1 2D0 2Q 74LS153 1S A1 1D3 1D2 1D1 1D0 1Q GND • 三、实验内容 • A、熟悉74LS153逻辑功能并测试 • Q=S(A1A0D0+ A1A0D1+ A1A0D2+ A1A0D3) • B、用双4选1数据选择器74LS153产生1011序列信号 • 1、真值表 • CP1=A0 • CP2=A1 • 1 0 1 1 • 接LED或示波器 • 1、使用LED观察时选用较低的CP频率如:2HZ、4HZ • 2、当使用示波器观察时要用较高的CP频率如:10KHZ、20KHZ。

2、译码器 • 译码器是一个多输入、多输出的组合逻辑电路。它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路或多路有信号输出。译码器在数字系统中有广泛的用途,不仅用于代码的转换、中断的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。现以74LS138为例进行应用设计。 • C、熟悉74LS138逻辑功能并测试 • D、用74LS138设计一个判定电路 • S1为主判,A2、A1、A0为三个副判 • 1、真值表:

& & & • 2、电路图: • S 或 • 输入逻辑 接LED • 开关 • 接LED S1 Y0 S2 Y1 Y2 S3 Y3 A2 Y4 A1 Y5 A0 Y6 Y7 &

四、实验要求 • 1、熟悉数据选择器和译码器的工作原理; • 2、用数据选择器和译码器对实验内容进行预设计; • 3、根据实验任务,画出所需的实验线路及记录表格。 • 五、实验报告 • 1、用数据选择器对实验内容进行设计、写出设计全过程、画出接线图、进 • 行逻辑功能测试;总结实验收获、体会。 • 2、画出实验逻辑线路图,描绘观察到的波形,并标上对应的地址码。 • 3、记录实验数据并对实验结果进行分析、讨论。

(2)3—8译码器74LS138 • 74LS138是3--8线译码器,其中A0 、A1、A2为地址输入端,~为译码输出端,S1 、S2 、3为使能端。当S1=1,S2+S3=0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。当S1=0 、S2+S3=X或S1=X、 S2+S3=1时,译码器被禁止,所有输出同时为1。 • 表 3-2.2 74LS138功能表 输 入 输 出 • S1 S2+S3 A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 • 1 0 0 0 0 0 1 1 1 1 1 1 1 • 1 0 0 0 1 1 0 1 1 1 1 1 1 • 1 0 0 1 0 1 1 0 1 1 1 1 1 • 1 0 0 1 1 1 1 1 0 1 1 1 1 • 1 0 1 0 0 1 1 1 1 0 1 1 1 • 1 0 1 0 1 1 1 1 1 1 0 1 1 • 1 0 1 1 0 1 1 1 1 1 1 0 1 • 1 0 1 1 1 1 1 1 1 1 1 1 0 • 0 × × × × 1 1 1 1 1 1 1 1 • × 1 × × × 1 1 1 1 1 1 1 1

VCCY0 Y1 Y2 Y3Y4 Y5Y6 74LS138 A0 A1 A2S2 S3 S1 Y7 GND

实验四 触发器及其应用 • 一、实验目的 • 1、掌握基本RS、D、JK、T和T’触发器的逻辑功能 • 2、掌握集成触发器的逻辑功能及使用方法 • 3、熟悉触发器的应用

二、设计原理 • 1、触发器具有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存贮器件,是构成各种时序电路的最基本逻辑单元。触发器有三种输入端,第一种是直接置位、复位端,用Sd和Rd表示,在Sd =0、 Rd =1或( Rd =0、 Sd =1)时,触发器将不受其它输入端所处状态的影响,使触发器直接置“1”(或置“0”);第二种是时钟脉冲输入端,用来控制触发器发生状态更新,用CP表示;第三种是数据输入端,它是触发器状态更新的依据。 • 集成触发器的应用广泛,它不但能组成数字电路的各种逻辑部件,如寄存器,计数器,还可用来产生脉冲波形以及对脉冲波形进行分频,倍频等。

三 、设计任务 • A、触发器功能测试 • 1、测试基本RS触发器的逻辑功能 • 按图接线,输入端、接逻辑开关,输出端Q接逻辑 电平显示输入插口,按表要求测试并记录。 • 2、测试双D触发器74LS74的逻辑功能 • (1)测试 Sd 、 Rd的置位、复位功能 • Sd 、Rd 、D接逻辑开关,CP接单次脉冲源,Q接LED显示输入插口。当 Sd =0 、 Rd =1或 Rd =0 、 Sd =1时任意改变D及CP的状态,观察Q端状态。自拟表格并记录之。 • (2)测试D触发器的逻辑功能 • 按下表逐项测试D触发器的逻辑功能,并指出 CP脉冲作用边沿。其状态方程为: Qn+1 = D

(3)用示波器测试D触发器的逻辑功能 • CP=10KHZ D=1KHZ 观察并描绘CP与Qn波形。 • 3、测试双JK触发器74LS112逻辑功能 • (1) 、测试Sd 、Rd的置位、复位功能 • 测试方法同实验内容2、(1) • (2)、测试JK触发器的逻辑功能 • 按下表逐项测试JK触发器的逻辑功能,并指出 CP脉冲作用边沿。JK触发器的状态方程为: • Q n+1= JQn+KQ n • (3)、用示波器测试JK触发器的逻辑功能: • CP=1KHZ J=K=1,JK触发器转换为T触发器。观察并描绘CP与Qn波形。

例:初态的设置方法 • 1、当Qn=0时,先将 Sd、Rd接输入逻辑开关,先使Sd、Rd都置 高电平为“1”,将 Rd拨置低电平为“0”,这时Qn=0,要使触发器受其它输入端状态的控制,必须使Rd由低电平“0”拨置高电平“1” • 完成当前初态的设置。操作 Sd→1、Rd→1→0→1。 • 2、当Qn=1时,先将 Sd、Rd接输入逻辑开关,先使Sd、Rd都置 高电平为“1”,将 Sd拨置低电平为“0”,这时Qn=1,要使触发器受其它输入端状态的控制,必须使Sd由低电平“0”拨置高电平“1” • 完成当前初态的设置。操作 Rd→1,Sd→1→0→1。 • 单脉冲的使用方法 • 1、正单脉冲 • 2、负单脉冲 • 例:波形CP: • D: • Q:

三、实验预习要求 • 1、复习有关触发器内容。 • 2、列出各触发器功能测试表格。 • 3、触发器实现正常功能时, Sd 、 Rd、应处于什么状态? • 4、用示波器观察触发器状态时,CP脉冲如何选择?触发器输入端如何设置? • 四、实验报告 • 1、试述各类触发器的逻辑功能。 • 2、总结观察到的各信号波形之间的相位关系,说明触发器的触发方式。 • 3、体会触发器的应用。

实验五 计数器及其应用 • 一、实验目的 • 1.掌握中规模集成计数器的使用及功能测试方法; • 2.计数器构成1/N分频器 ; • 3.学习用集成计数器构成模N的方法。

VCC D0 CR BO COLD D2 D3 74LS192 D1 Q1 Q0 CPD CPU Q2 Q3 GND • 二、设计原理 • 1、74LS192同步十进制可逆计数器的管脚及其功能: • LD置数端D0、D1、D2、D3计数器输入端 • CR清除端Q0、Q1、Q2、Q3数据输出端 • CPU加计数端CO非同步进位输出端 • CPD 减计数端BO非同步借位输出端

74LS192逻辑图 2、74LS192逻辑功能表: 输 入 输 出 • CR LD CPUCPD D3 D2 D1 D0 Q3 Q2 Q1 Q0 • 1 × × × × × × × 0 0 0 0 • 0 0 × × d c b a d c b a • 0 1 ↑ 1 × × × × 加 计 数 • 0 1 1 ↓ × × × × 减 计 数 • 异步预置: 加计数 预置值= N -M-1 加计数复位接线Q3Q2Q1 Q0 • 减计数 预置值= M 加计数预置接线 时钟 脉冲 CPUCOCO 1 CPD BO • 1 CR LD LD • 同步预置:加计数 预置值= N -M • D3 D2 D1 D0为预置端口 • 减计数 预置值= M -1

3、实现任意进制计数 • (l)用复位法获得任意模值的计数器 假定已有N进制计数器,而需要得到一个M进制计数器时, 只要M < N,用复位法使计数器计数到M时置“0”(输出反馈 接CR口),即获得M进制计数器。 • (2)利用预置法获M模值的计数器 通过设置不同的预置值,使计数器从某个预置状态开始计数,到达模值为M时的终止状态时,产生预置控制信号,加到预置控制端LD进行预置,这时计数器的工作过程为:预置→计数→预置→计数。(由 D0、D1、D2、D3计数器输入端进行预置,输出反馈至LD口,注意:由于CP为同步时钟脉冲而CO(非同步进位输出端)输出反馈信号至LD口进行预置跟CP信号不同步因此CO输出反馈要经过两个非门至LD口延迟后完成预置计数)。

三、实验内容 • 2、测试74LS192同步十进制可逆计数器的逻辑功能 • 计数脉冲由单次脉冲源提供,清除端CR 、置数端、数据输入端D0 、D1 、D2 、D3分别接逻辑开关,输出端Q0 、Q1 、Q2 、Q3接译码显示输入相应插口A、B、C、D;和接逻辑电平显示插口。逐项测试并判断该集成块的功能是否正常。 • 3、采用74LS192可逆计数器,分别用复位法及预置法设计模N计数器,并进行测试及用示波器观察输入输出波形。

四、实验中易出现的问题 • 1、对计数器芯片的功能引脚理解不够,如LD、CR、CO、BO这些引脚的功能和特点要详细介绍。 • 2、 容易混淆计数器的几种工作状态,它们有:复位状态、预置状态、计数状态。其中各种状态对其相应的功能引脚的设置也不同。 • 3、 在用预置法做任意模值计数器时,要在反馈端加入一定的延时电路,如取两次反。这样之后工作才会稳定。 • 五、实验报告 • 1、绘出各项实验内容的详细线路图。 • 2、画出实验线路图,记录实验所得的有关 CP,Q点波形(Q为对应模值点的波形)。对实验结果进行分析。 • 3、总结使用集成计数器的体会。

实验六 脉 冲 电 路555时基电路及其应用 • 一、实验的目的 • 1、熟悉555型集成时基电路结构、工作原理及其特点 • 2、掌握555型集成时基电路的基本应用 • 3、熟悉芯片及各管脚功能。

二、555电路的工作原理 • 555电路的内部电路组成如图 8―1所示。它含有两个电压比较器,一个基本RS触发器,一个放电开关管T,比较器的参考电压由三只5KΩ的电阻器构成的分压器提供。它们分别使高电平比较器A1的同相输入端和低电平比较器A2的反相输入端的参考电平为 VCC和 VCC 。A1与A2的输出端控制RS触发器状态和放电管开关状态。当输入信号自6端输入并超过参考电平 2/3VCC时,触发器复位,555的输出端―3端输出低电平,同时放电开关管导通。当输入信号自 2端输入并低于1/3VCC时,触发器置位,555的3 端输出高电平,同时放电开关管截止。是复位端(4端),当=0时,555输出低电平。平时端开路或接VCC 。VC是控制电压端(5端),平时输出Vcc作为比较器A1的参考电平,当5端外接一个输入电压,即改变了比较器的参考电平,从而实现对输出的另一种控制,在不接外加电压时,

通常接一个0.01uF的电容器到地,起滤波作用,以消除外来的干扰,以确保参考电平的稳定。通常接一个0.01uF的电容器到地,起滤波作用,以消除外来的干扰,以确保参考电平的稳定。 • T为放电管,当T导通时,给接于7端的电容器提供低阻放电通路。 • 555定时器主要是与电阻、电容构成充放电电路,并由两个比较器来检测电容器上的电压,以确定输出电平的高低和放电开关管的通断。利用它可以构成从微秒到数十分钟的延时电路、单稳态触发器、多谐振荡器、施密特触发器等脉冲产生或波形变换电路。 • 等。原理图如下所示。

& C1 C2 & & & • 555原理框图: • VCC RD • 84 • 5K • VCO VR1 VC1 G1 5Q • VI1 6 • 5K • VI2 2 VC2 3VCO • VR2 G2 QG3 G4 • 5K • VO’ 7 TD • 1

三、实验设备与器件 • 1、数电实验台 • 2、双踪示波器 • 3、555一片、 电位器、电阻、电容若干