Understanding Paging in Virtual Memory Management

This chapter delves into the concept of paging as a method to virtualize memory, addressing the challenges of segmentation, such as external fragmentation and space management. It outlines the mechanics of paging, including the structure of page tables and the process of address translation from virtual to physical memory. The chapter highlights the advantages of paging, such as flexibility and simplicity, while acknowledging its drawbacks, including slower access times and potential memory waste due to page table storage. It provides examples to illustrate the operational details of paging mechanisms.

Understanding Paging in Virtual Memory Management

E N D

Presentation Transcript

Chapter 18Paging Chien-Chung Shen CIS, UD cshen@cis.udel.edu

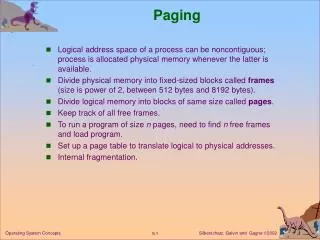

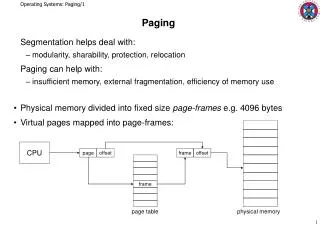

Introduction • Our goal: to virtualize memory • Segmentation (generalization of dynamic relocation) can do it, but has issues • managing free space with external fragmentation • Fixed vs. variable sized units • Paging: virtualize memory without segmentation • e.g., 64-byte address space with 4 pages

Paging • Page frame in physical memory • Advantages: • flexibility– works, no matter how process uses its address space • simplicity of free space management • How to record where each virtual page is placed in physical memory? • per-process page table

Address Translation • Split address into virtual page # (VPN) and offset • 64-byte address space • page size = 16 bytes • VA 21 • VPN indexes page table to get physical frame # (PFN) • offset stays the same

Where Are Page Tables Stored • 32-bit address space with 4KB pages • 20-bit VPN and 12-bit offset • 4 bytes per page table entry (PTE): 4MB = 4×220 • page tables are stored in “kernel” memory

Structure of Page Table • Linear page table (an array) • OS indexes the array by VPN to get PFN • Bits associated with each PTE • valid • protection: for R, W, X • present • dirty • reference (access)

Paging Is Too Slow movl 21, %eax • To fetch data in virtualaddress 21, translate21 intophysicaladdress (117) • fetch PTE (in memory) to performtranslate • whereisthepage table fortherunningprocess? • page-table base register: physicaladdressofthestartinglocationofthepage table VPN = (VirtualAddress & VPN_MASK) >> SHIFT PTEAddr= PageTableBaseRegister + (VPN * sizeof(PTE)) • VPN_MAST = 110000 and SHIFT = 4 • hardware fetches PTE frommemory to get PFN and concatenateitwithoffset fromthevirtualaddress to formthedesiredphysicaladdress offset = VirtualAddress & OFFSET_MASK PhysAddr= (PFN << SHIFT) | offset • hardware fetchthedesired data frommemory and putitintoeax

Summary // Extract the VPN from the virtual address VPN = (VirtualAddress & VPN_MASK) >> SHIFT // Form the address of the page-table entry (PTE) PTEAddr= PTBR + (VPN *sizeof(PTE)) // Fetch the PTE PTE = AccessMemory(PTEAddr) // Check if process can access the page if (PTE.Valid == False) RaiseException(SEGMENTATION_FAULT) else if (CanAccess(PTE.ProtectBits) == False) RaiseException(PROTECTION_FAULT) else // Access is OK: form physical address and fetch it offset = VirtualAddress & OFFSET_MASK PhysAddr= (PTE.PFN << PFN_SHIFT) | offset Register = AccessMemory(PhysAddr) For every memory reference (whether an instruction fetch or an explicit load or store), paging requires to perform one extra memory reference in order to first fetch the translation from the page table

Memory Trace int array[1000]; for (i = 0; i < 1000; i++) array[i] = 0; $ objdump –d a.out 0x1024 movl $0x0,(%edi,%eax,4) // move 0 into VA of array[edi]+4*[eax] 0x1028 incl %eax 0x102c cmpl $0x03e8,%eax // 0x03e8 = 1000 0x1030 jne 0x1024 • Virtual address space of size 64 KB and page size 1 KB • Each instruction fetchgenerates 2 memory references: one to page table to find the physical frame that the instruction resides within, and one to instruction itself to fetch it to the CPU for processing • movladds another page table access and then the array access itself

Memory Trace of 1st 5 Loops • Page table: PA 1024 • Code: VA 1024-1030 • Array: VA 40000 to • 44000 (VPN 39-42) • Page table: • VPN 1 -> PFN 4 • VPN 39 -> PFN 7 • VPN 40 -> PFN 8 • VPN 41 -> PFN 9 • VPN 42 -> PFN 10

Summary • Advantages (over segmentation) • no external fragmentation (with fixed sigze pages) • flexible to enable the sparse use of virtual address spaces • Disadvantages • slow (extra memory accesses to access the page table) • memory waste (with memory filled with page tables instead of application data)