计算机系统结构

810 likes | 985 Views

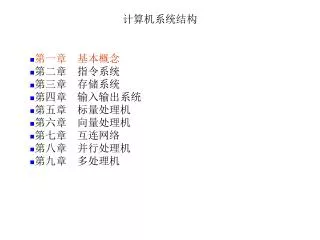

计算机系统结构. 胡伟武. 提 纲. 计算机的基本概念 影响计算机设计的主要因素及其发展趋势 计算机性能 计算机成本 计算机功耗 实际机器的性能和性价比的衡量. 超级服务器. 打印机扫描仪. 服务器. 防火墙. 交换机. 路由器. 终端设备. Internet. 工作站. 什么是计算机? — 现代信息系统. Internet. 游戏机. DVD. 可视电话. 手机. 家庭网络. 家庭网关. 掌上电脑. MP3. 数码相机. 数字电视. 什么是计算机? — 数字化生活. 高性能计算应用举例.

计算机系统结构

E N D

Presentation Transcript

计算机系统结构 胡伟武

提 纲 • 计算机的基本概念 • 影响计算机设计的主要因素及其发展趋势 • 计算机性能 • 计算机成本 • 计算机功耗 • 实际机器的性能和性价比的衡量

超级服务器 打印机扫描仪 服务器 防火墙 交换机 路由器 终端设备 Internet 工作站 什么是计算机?—现代信息系统

Internet 游戏机 DVD 可视电话 手机 家庭网络 家庭网关 掌上电脑 MP3 数码相机 数字电视 什么是计算机?—数字化生活

高性能计算应用举例 • 核武器数值模拟全面核禁试条约签订后, 核武器的数值模拟成为唯一可能进行的全系统试验。这种水平的模拟所需要进行的计算远远超过了目前所能达到的水平。据估计, 美国为了满足2010 年核武器库管理的需求,需要每秒运算 1016-17 次的计算机。

高性能计算应用举例 • 流体力学 喷气式飞机在超音速飞行时的颤动分析要同时计算463674个非线性流体方程,45108个线性结构方程,这些方程要计算成千上万次。计算由 Cray T3D,IBM SP-2, Intel Paragon XP/S三台高性能计算机共同完成。飞机各部分应力的大小可用不同的颜色表示,红色表示应力大,蓝色表示应力小。

现在的计算机中为什么用二进制? 计算机是由电子元器件构成的,二进制最易实现。

二进制的由来 • 莱布尼兹是欧洲最早发现二进制的数学家 • 冯.诺依曼最早将二进制引入计算机应用, • 计算机中的数据和程序都采用二进制。 莱布尼兹为奥古斯特公爵制作的二进制纪念章 • 中国在公元前2000多年伏羲氏就发明了八卦, • 是用—和--两种符号拼出来的 ,是世界上最古老 • 的二进位制。

(3×4) + (5×7)? • 3 ×4 =12 • 5 ×7=35 • 12+35 = 47

内 存 CPU • 4 5 7 • 读取 3 • 读取 4 • 两数相乘 • 存入结果1 • 读取 5 • 读取 7 • 两数相乘 • 存入结果2 • 读取结果1 • 读取结果2 • 两数相加 • 存入结果 12 35 47 读取结果1 读取结果2 读取 7 两数相乘 存入结果2 读取 5 两数相加 两数相乘 读取 4 存入结果 读取 3 存入结果1 5 3 × × 4 7 = 12 = 35 35 = 47 12 + 冯诺亿曼结构:数据和程序都在存储器中,CPU从内存中取指令和数据进行运算并把结果也放到内存中

数据线 外存储器 控制线 输入设备 输出设备 内存 运算器 控制器 CPU 冯诺依曼结构

计算机怎样才能跑得快 用最少的指令描述一件事情 --算法,编译 每拍做更多的事情 --体系结构 提高‘芯’跳的速度 --主频

是不是 跑得快 就行了呢?

这些大家伙具有战略意义 分秒必争,目的就是越快越好!

电脑越来越普遍 要让更多人买得起,价格就很重要了

无处不在的CPU 电池怎样才能用得久呢?

高性能计算机的功耗 • 美国为了满足2010 年核武器库管理的需求,需要每秒运算 1016-17 次的计算机 • 如果10亿次计算机的功耗是100瓦(想想PIV的功耗)100万( 1014 )亿次计算机的功耗是1000万瓦

什么是计算机系统结构? • 50-60年代 • Computer Architecture=Computer Arithmetic • 70-80年代 • Computer Architecture=Instruction Set Design • 90年代以后 • Computer Architecture=Design of CPU, Memory System, I/O System, Multiprocessors • Searching the space of possible designs at all levels of computer systems

应用、操作系统、编译系统 计算机系统结构(性能、价格、功耗) 逻辑设计、电路设计、工艺制造 上知天文、下知地理 • 计算机系统结构的位置 • 居于系统软件和逻辑电路之间 • 从界限清晰到界限不清晰 • ISA:RISC、CISC=>Transmeta、Itanium、虚拟机 • 逻辑和电路:晶体管=>晶体管+连线

地理:硬件实现技术的发展趋势 • 以下四种飞速发展的实现技术对现代计算机实现的影响最为深远 • 集成电路逻辑技术 • 半导体DRAM:增长速度缓慢,形成Memory Gap • 磁盘存储技术 • 网络技术:对高性能计算影响巨大 Capacity Speed (latency) Logic 2x in 3 years 2x in 3 years DRAM 4x in 3 years 2x in 10 years Disk 4x in 3 years 2x in 10 years

从机房、机柜、板卡到芯片 109丙机,我国自行研制的晶体管大型通用数字电子计算机 104机,我国第一台大型通用数字电子计算机 103机,我国第一台小型通用数字电子计算机 龙芯1号,我国自行研制的第一个通用微处理器 757机,大型向量中规模集成电路数字电子计算机 KJ8920大型计算机系统

Moore引导的CPU发展 • CPU:Central Processing Unit • 中央处理器(控制器+运算器),简称处理器 • 1940’s,有了计算机,就有CPU(几个机柜) • 芯片:集成电路 • 1960’s,开始有芯片,CPU是由多块板子构成 • CPU芯片:把完整的CPU做在一块芯片上 • 1970’s,开始有简单的CPU芯片 • 1980’s以来,内存存储器的地位日益重要 • Moore定律:每1.5年CPU主频和内存容量增加1倍 • 但内存速度增加慢,1GHz的处理器访问内存需要几十到几百拍 • 现在的CPU芯片:控制器+运算器+部分存储器 • SOC:System-on-Chip,片上系统 • CPU是SOC的核心(core)

世界半导体行业共同制订的2003年国际半导体技术发展路线图(MPU)世界半导体行业共同制订的2003年国际半导体技术发展路线图(MPU) 性价比合理MPU面积:140mm2高性能MPU面积:310mm2 预计到2018年,主频可达53.2GHz

系统结构与摩尔定律 • 系统结构的双重作用 • 根据Intel公司的资料,从486到Pentium 4,频率提高了50多倍(其中13倍来自工艺的改进、4倍来自结构的改进),性能提高了75倍多(其中13倍来自工艺的改进、6倍多来自结构的改进)。 • 根据路线图对历史数据的分析,每代微处理器最大的片内时钟频率是上代产品的两倍,其中1.4倍来源于器件的按比例缩小(它最终要受氧化层厚度和其它因素限制),另外1.4倍来源于流水级中逻辑链长度(或逻辑门数目)的减少(如180纳米节点时是32个等效4扇出反相器的延迟,而在130纳米时只有26个等效4扇出反相器延迟)。

线宽按比例缩小,集成度指数增加 • 摩尔定律不是性能规律 • 按比例缩小导致性能同步增长的趋势在130纳米时已经终止了 • 栅氧厚度 • 连线延迟 • 工作电压 Classical Scaling:性能也按摩尔定律指数增长吗? Innovation. That will be the driver of performance, rather than scaling.

摩尔定律关于主频部分的终结 • 不可能使用少于6-8个等效4扇出反相器产生出波形好的时钟脉冲; • 流水线结构的效率会越来越低;最新的预测表明,最小可实现的逻辑深度近似于10-12个四扇出反相器延迟。考虑到控制流水线的锁存器(latch)本身的延迟,在这种情况下,实际留给有效处理工作的逻辑只剩下了6-9级FO4。 • 由封装承受能力引起的热包封限制使得难以实施很深的互连流水线结构; • 结构和电路的创新将越来越多地用于减轻给互连RC效应带来的不良影响而不太可能直接改善频率响应。

如何有效利用晶体管资源? • 晶体管数量剧增 • 晶体管种类增多 • 逻辑与DRAM的集成 • 如何把资源投向高回报的部分 • 取并执行更多的指令 • 片上集成多个处理器 • 增大片上存储器 • 集成更多的外围电路 • … … • 设计复杂度增加 Pollack’s Rule:两代处理器结构之间,性能的增长率大致只是晶体管数增长率的平方根

连线延迟变长,怎么办? • 晶体管开关速度快了,但信号传输没有变快 • 局部线延迟不变(变细了,但也变短了) • 全局的连线延迟还会不断变长(芯片面积不变) • 30nm时,一个时钟周期信号只能穿过芯片的1% • 目前设计中需要全局连线的部分都不可扩展 • 如单CPU里的全局寄存储器、forwarding、… … • 全局的时钟信号如何处理? • 强调:局部化、流水化、异步、自定时 • 不可能无限止细分流水线:大于10-12 FO4

功耗的作用 • 由于晶体管的特性,以后工作电压不会随着工艺进步而降低,加上频率提高,导致功耗密度随集成度增加而增加 • 沿用目前设计思路,再经过几代,每cm2功耗可能达到1000W • Intel暂不推出4GHz以上的P4 • 需要降低工作电压来降低功耗,但随着阈值电压的降低漏电功耗大大增加

风扇大大降低了系统可靠性 • 重量:700克以上 • 转速:7000转/分 • 跟硬盘差不多 • 功耗:3.5瓦 • 成本:$40 • 噪音:55-60db • MTBF: 2-3年

天文:应用的影响 • 应用随时间的迁移 • 科学和工程计算、事物处理、网络服务和媒体应用 • 应用越来越广:桌面、服务器和高性能机、嵌入式 • 桌面电脑 • 焦点:性价比 • 服务器及高性能计算 • 焦点:稳定性以及计算能力 • Google、BlueGene • 嵌入式计算机 • 焦点:低功耗以及实时计算 • 各种移动终端、智能设备

应用特性正在发生变化 • 过去:运算速度很重要 • Linpack,Dhrystone,Whetstone • 现在:均衡的性能 • SPEC CPU 2000:定点、浮点、I/O、大内存 • TPC:专注I/O性能(尤其是磁盘I/O) • 未来:以低能耗处理大量的服务 • 网络、媒体为代表的流(stream)的处理 • 基于WEB的大量请求的快速处理 • 还没有形成有代表性的基准程序 • 结构上也没有形成标准

应用变化要求结构相应地改变 • 如何加速单个控制流的执行过程 • 现在:复杂的硬件(流水、乱序、预测、猜测、调度),导致巨大的能耗 • 未来:天然并行的WEB服务请求,简单的并行 • 如何缩小运算与访存的速度差距 • 过去:用cache,面积(成本)和能耗的增长 • 未来:流式数据,只用一次,cache不管用 • 需要有新的结构来解决这个问题

应用多样性意味着芯片的多样性? • 芯片的制造成本降低,但NRE在不断增长 • 设计复杂性:资源(人力)、时间、返工 • 掩膜制备费用的增长 • 芯片的产量必须增长,才能有效分摊NRE • 芯片种类不能多、芯片的生存周期应该拉长 • 与应用复杂多变、产品更新换代快的需求相矛盾 • 谁更有前途:通用处理器 vs. ASIC/SOC • 通用处理器的结构需要变得更灵活、可根据应用的需要进行重构

小结:计算机发展的趋势 • 处理器结构以20年为周期,已经历了一个简单、复杂、简单、复杂的过程 • 即使摩尔定律真的能用到2018年,也已经大大放慢,尤其是处理器主频正和晶体管速度正在分道扬镳 • 连线延迟和设计复杂度越来越大,物理设计对结构的反作用越来越大 • 网络及媒体应用使处理器需求发生了变化 • 功耗问题日益突出:Performance per second, Performance per dollar, Performance per watt • 对处理器的微体系结构进行突破性变革的时机已经到来 • 多核结构符合上述发展趋势的要求 • 变革的时候也是后来居上的重要机会

性能、价格、与功耗 • CPU发展过程中,随着技术本身的发展和需求的变化,矛盾的主要方面在不断地变化 • Performance per second • Performance per dollar • Performance per watt • Intel受益于第一次变化,ARM受益于第二次变化 • 低功耗的研究已经成为学术界的研究热点,从低端的手机到高端的百万亿次高性能计算机,都对处理器的功耗提出了很高的要求 • 性能、价格、功耗的关系非常复杂,都是计算机系统结构设计需要考虑的内容 • 其它因素 • 体积、可靠性、稳定性、寿命 • 民用、工业用、军用、宇航用

计算机性能的评价 • 性能评价的标准 • 性能评价的公式 • 基准测试程序套件 • 性能评价报告 • 性能的比较与总结

Application Answers per month Operations per second Programming Language Compiler (millions) of Instructions per second: MIPS (millions) of (FP) operations per second: MFLOP/s ISA Datapath Megabytes per second Control Function Units Cycles per second (clock rate) Transistors Wires Pins 不同层次的“性能”

不同应用的性能 • 个人PC:单任务关注响应时间 • 计算中心:多任务关注吞吐率 • 程序运行时间的表示 • Wall Time • User Time+System Time

影响CPU性能的因素 • 性能的最本质定义 • 完成一个任务(如后天的天气预报)所需的时间 • 以指令为基本单位

CPI及IPC • 在指令系统确定后,系统结构设计者的主要目标就是降低CPI或提高IPC • 平均CPI“Average Cycles per Instruction” • CPI = (CPU Time * Clock Rate) / Instruction Count = Cycles / Instruction Count • Instruction Frequency

计算CPI的例子 Base Machine (Reg / Reg) Op Freq Cycles CPI(i) (% Time) ALU 50% 1 .5 (33%) Load 20% 2 .4 (27%) Store 10% 2 .2 (13%) Branch 20% 2 .4 (27%) 1.5 Typical Mix

减少指令数和提高IPC • 结构提高计算机性能的常用方法和原则 • 加快经常性事件的速度 • 局部性原理 • 利用并行性

加快经常性事件的速度 • 设计者要有“有所为,有所不为”的原则,有所取舍,优先考虑较长时间发生的事件。设计者必须清楚什么是经常性事件,以及提高这种情况下机器的运行速度对计算机的整体性能提高有多大贡献。 • Amdahl定律 • 通过使用某种较快的执行方式所获得的性能的提高,受可使用这种较快执行方式的时间所占的百分比例的限制

Amdahl定律举例 • 问题 • 浮点功能单元执行性能提高2倍;但是仅有10%的浮点指令。计算总体性能加速比 ExTimenew= ExTimeold x (0.9 + 0.1/2) = 0.95 x ExTimeold Speedupoverall= 1÷0.95=1.053

开发局部性 • 局部性原理 • 时间局部性 • 空间局部性 • 应用实例 • Cache • TLB • 预取

开发并行性 • 指令级并行 • 是过去的20年里体系结构设计者提升性能的主要途径 • 时间并行性:指令流水线 • 空间并行性:SuperScalar(Out-of-Order)和EPIC(编译器优化) • 进一步挖掘指令级并行的空间不大 • 数据级并行:SIMD • 向量机 • SSE多媒体指令 • 作为指令级并行的有效补充,仍然能在流媒体等领域发挥重要作用,在专用处理器中应用较多 • 线程级并行 • 线程级并行大量存在于Internet应用 • 多核处理器 • 多线程处理器 • 是目前的热点