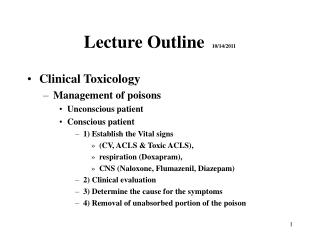

Lecture 14 10/14/11

560 likes | 728 Views

Lecture 14 10/14/11. Lab 4, contingent on covering interrupts Skip to chapter 11, Interrupts: read 422-466; also read section 8.6 on software interrupts Finish reading chapter 6 (231-244) Read Chapter 7 (254-267) (lecture divisions a bit arbitrary after the fact!). Listing File: TheList.rtf.

Lecture 14 10/14/11

E N D

Presentation Transcript

Lecture 14 10/14/11 • Lab 4, contingent on covering interrupts • Skip to chapter 11, Interrupts: read 422-466; also read section 8.6 on software interrupts • Finish reading chapter 6 (231-244) • Read Chapter 7 (254-267) (lecture divisions a bit arbitrary after the fact!)

Listing File: TheList.rtf • location of each source line in memory • cycle-by-cycle information • object code paired with corresponding assembly source

Pseudo-ops in TExaS • Most confusing part of assembly language programming • instructions (opcodes) are fixed in hardware by Motorola/Freescale • pseudo-ops can vary with each assembler program written to support the architecture • so different 68HC11 assemblers will support different pseudo-ops and different syntax for same • TExaS supports multiple “standard” pseudo-op dialects

set vs. equ • Both assign a value to a label size equ 5 I set 0 • equ cannot be reassigned later, set can be reassigned later • permits name “I” to be used in more than one subroutine for instance without conflict • while “size” will be a global (permanent) label • equ prohibits forward references or undefined symbols in expressions, set allows them (but still probably not a good idea!)

;6811: sum a vector org 0 size equ 5 data rmb size org $F000 sum ldaa #size ldx #data clrb loop addb 0,x inx deca bne loop rts ;6812: sum a vector org $800 size equ 5 data rmb size org $F000 sum ldaa #size ldx #data clrb loop addb 1,x+ dbne A,loop rts equ example decrement and branch if not equal Both omit initializing data!

;6811 ;binding phase I set 0 J set 1 ;allocation phase function pshx ;save old X des ;alloc I des ;alloc J tsx ;create fp ;access phase clr I,x ;Clear I ldab I,x ;RegB=I staa J,x ;J=RegA ;deallocation phase ins ;dealloc J ins ;dealloc I pulx ;restore old X rts ;6812 ;binding phase I set 0 J set 1 ;allocation phase function leas -2,sp ;alloc I,J ;access phase clr I,sp ;Clear I ldab I,sp ;RegB=I staa J,sp ;J=RegA ;deallocation phase lease 2,sp ;dealloc ;I,J rts set example: local (automatic) variables

fcc/fcb Strg1 fcc “happy” fcb 0 or Strg2 fcb “happy”,0 (Why the zero?)

rmb/ds: reserve multiple bytes xval rmb 1 reserve 1 byte named xval for later use (not “initialize xval to 1!) arrayx rmb 20reserve 20 byte array with origin name arrayx

Chapter 5 – I/O programming • Device Drivers • simply a collection of software functions that allow higher level software to use an I/O device via a consistent interface. • chapter 5 covers software interface • chapter 6 covers physical interfacing issues • note differences between I/O in protected (OS) environment and embedded environment.

Example: Port A In assembler, PORTA equ $1000 and in C, #define PORTA *(unsigned char volatile *)(0x1000) why volatile?!?

Port internals • Fig 5.2 p 178 – simple vs. latched ports

Ports - recap • Latched or not (i.e. PortC): • Latched port records input transitions on a certain edge of a certain control signal • Simple (non-latched) port always reflects current value of inputs (level sensitive) • Readable output ports or not • last value written to output port can be latched (or not) so you can read the output port (or not!) • alternative is “write-only output port” • PortC: simple or latched, readable output or read-only (input), per pin.

Serial Communications • Serial ports send/receive 1 bit at a time • bits per second == Baud rate • You could design your own proprietary serial signaling strategy using “bare” input/output pins, but… • Motorola has built-in SCI (Serial Communications Interface) to simplify structured serial communications, as with RS-232; uses PortD on 68HC711E9. • you can see on your boards that the on-board RS-232 connector is connected to PortD pins, pins D0 and D1. • coupled through an RS-232 level shifter chip (U8 – HIN232CP) directly to port pins to get voltages from 0-5VDC to -12/+12VDC.

HIN232CP • Generates +/-12VDC from 5V input (well +/-10VDC) with on-board charge pump, 4 large-ish external capacitors

RS-232 • Defines 25 signals, only 3 really needed • Tx, Rx, GND • many hardware flow-control signals can be used but are not needed, software flow control works fine with adequate buffers • SCI internals to implement RS-232 • Baud-rate control register • divides internal clock down to desired rate • if you change EClock, you corrupt Baud rate! • Mode bit “M” (8 or 9 bit frames – no parity/parity) • Critical: NO GLOBAL CLOCK! Each serial device generates its own local clock. • no clock signal on cable!

Old School RS232 Delete: clocking, second channel, handshaking From http://www.lammertbies.nl/comm/cable/RS-232.html

Axiom Serial Port • Strictly speaking, your board follows EIA-574 and not RS-232: This maps the most common of the 25 RS-232 pins onto the 9-pin D-Shell connector and uses RS-232 voltage levels (+/- 12V). • (Somewhat archaic) Nomenclature: • DTE: Data Terminal Equipment (Computer or terminal or printer – source or sink in some sense • DCE: Data Communications Equipment (modem – pipe in some sense) • Null modem to connect DTE to DTE (crossed wired: Tx-Rx, Rx-Tx) • straight-through wiring for DTE to DCE (Tx-Tx, Rx-Rx) • (DCE “receives” on transmit line, transmits on receive line – Terminal point of view!)

Serial Frame • 1 Start bit (a logic “0”) • 8 or 9 data bits, LSB first (9=parity if used) • 1 stop bit (a logic “1) • Example with M=0 (no parity) • Bandwidth in bytes per second is roughly Baud rate divided by 10 • 56K modem: 5,600 bytes per second. Sta B0 B1 B2 B3 B4 B5 B6 B7 Sto

Asynchronous transmission • Without global clock, RS-232 is asynchronous: receiver never knows when a new frame will arrive. • Key: inside 68HC11, SCI: 10/11 bit “transmitter shift register” (TSR) • not directly accessible, but its output is the TxD signal with TTL levels (0-5V) • we write to SCDR – “Serial Communications Data Register” – to get data into this shift register for sending; start/stop bits automatically added. • SCDR is write-only, i.e. you can’t re-read value sent • (also a separate receive shift register – later!)

Thermometer postmortum • Display brightness • Power consumption • Flicker • Data resolution

Transmission details (M=0/1) Stop 7 6 5 4 3 2 1 0 Start TxD (PD1 on HC11) Shift Clock 1 Data 0 SCDR (8 bits) Write SCDR Stop Par 7 6 5 4 3 2 1 0 Start TxD (PD1 on HC11) Shift Clock 1 T8 Data 0 SCDR (8 bits) Write SCDR

Fine-grain control • Set TE bit to Enable Transmission (turn on SCI) • Set SBK (Send Break) to 1 to send a block of 10/11 zeros to wake up a receiver if needed • Arm interrupts by setting TIE (Transmit Interrupt Enable) – later! • Transmit Complete Enable control bit (TCIE) allows TC flag to generate interrupts • TDRE (Transmit Data Register Empty) flag is set when SCDR is empty; cleared by reading TDRE flag and then writing to SCDR. • TC (Transmit Complete) flag is set when transmitter shift register is empty; cleared by reading TC flag then writing to SCDR. • i.e. TDRE: nothing left to send, TC: transmit shift register is done shifting

Queue behavior • Essentially, SCDR and Transmit Shift Register act as 2-entry queue: current byte being sent is in Transmit Shift Register, next byte to be sent is staged in SCDR. • if data already in TSR, SCDR will wait before transferring • Most “real” serial ports put a larger (16 entry or so) hardware FIFO in front of the Transmit Shift Register equivalent to keep serial channel busy • gives software more slack in responding to interrupts as well!

Receiving end – mirror image (roughly!) • Receive shift register has a separate SCDR, at same address as transmit SCDR (!), but read-only instead of write-only • Tricky bit: must synchronize receive shift register with incoming data • requires prior knowledge of sender’s baud rate • manual setting or auto negotiate • requires local clocks to be not too inaccurate!

Control bits for receiver • RE: Receiver enable: turn on receiver • RWU: Receiver Wakeup • if 1, a receiver input will wake up the computer out of low power sleep mode • RIE: Receiver interrupt enable: enables RDRF flag to request interrupts • ILIE: Idle Line Interrupt Enable: enables IDLE flag to request interrupts • RDRF: Receive Data Register Full: set when new input data are available; clear by reading RDRF and reading SCDR (to capture incoming byte) • IDLE: Receiver Idle Flag: set when receiver line is idle; cleared by reading IDLE flag and reading SCDR • OR: Overrun flag: set when input data are lost because previous frame was not read in time • NF: Noise flag: set when input is noisy • each bit is sampled 3 times by receiver; if not unanimous, NF set. • FE: Framing Error: stop bit wrong! • NF and FE usually due to mismatched baud rate

Receiver operation • Receiver waits for 1-0 transition indicating new Start Bit is inbound, then shifts in 10/11 bits of data 1 at a time from RxD line 7 6 5 4 3 2 1 0 RxD (PD0 on HC11) Shift Clock 1 R8 Data 0 SCDR (8 bits) Read SCDR

Receiver operation • Start bit arrives • 10/11 bits shifted in • Start/Stop bits removed after noise/framing checks • 8 data bits loaded into SCDR • if M=1 9th bit loaded to R8 (and parity checked) • RDRF is set • If SCDR is already full from previous byte, receiver delays loading until SCDR is read by software • If third byte starts to arrive before SCDR is read, overrun error

Overrun – note typo in some printings of book fig 5.9 • Overrun occurs 10 bit times after setting RDRF=1 if data continue to arrive and software does not read incoming bytes. • 6812: similar details; most models have 2 built-in serial ports

Software for serial comms • Cries out for interrupt-driven approach (later), but section 5.3.5 gives 6811/12 code for polling serial I/O via the SCI (are we there yet?!?) • Polling approach requires each code to know when to expect incoming bytes since will busy wait • Program 5.7 p. 189

Alternate serial comm approach: SPI • Synchronous Peripheral Interface • unlike SCI, “master” here will make common clock available to “slave” over the interface • 4 pins on PortD • PortD5: SS: Slave Select: Active-low select signal generated by master indicating channel is active • PortD4: SC1K: 50% duty cycle clock generated by master • PortD3: MOSI: Master Out/Slave In – serial comm data line • PortD2: MISO: Master In/Slave Out – serial comm data line

Using SPI • Details in Freescale docs and your book • set directions appropriately with DDRD • set bits in SPCR (SPI Configuration Register) to activate • SPSR (SPI Status Register) and SPDR (SPI Data Register) implement the interface

16-bit timer • 6811/12 both have 16-bit counter known as TCNT • increments at fixed rate so can be read to determine current time • can be used to create pulses, square waves, pulse-width modulated waves • can measure period, pulse width, or frequency of an input signal in combination with other 6811/12 features

TCNT details • occupies 2 registers since 16 bits: $100E and $100F • Counting rate programmable • bits PR1 and PR0 of TMSK2 – say whether to divide EClock by 1,4,8,16 giving periods of 500nS, 2-4-8µs accordingly • cyclic count; each overflow from $FFFF back to 0 sets the TOF bit, can fire an interrupt if TOI is set to 1

To precisely time a certain interval • of up to 32767 timer ticks (not always cycles), already stored in RegD Wait addd TCNT ; add current timer ; value to regD to determine ; desired end time wloop cpd TCNT ; compare current time ; to desired end time ; EndT-TCNT < 0 when EndT<TCNT bpl wloop rts So: delay of 10 in regD, current timer of, say, 467; D becomes 477, once TCNT reaches 478 result of cpd goes negative and timer returns

What if timer wraps around? • desired count 10, current time $FFFE; $FFFE + 10 = 8 • nb $FFFE = -2 as 2’s comp 8 – (-2) = pos … 8 – 7 = pos 8 – 8 = pos 8 – 9 = neg, timer returns

PortA secret identity: Pulse Accumulator • 2 modes: event-counting mode, gated time mode • Event Counting Mode: 8-bit count increments on either rising or falling edge (programmable) of PA7 at rates up to EClock/2 • Gated time accumulation mode: 8-bit count increments at (EClock/64) rate as long as PA7 is high (or low – configurable) • 32µs ticks at 2MHz

Pulse Accumulator • Can thus either count events or do frequency measurements • easy to measure pulse width this way • frequency: count number of falling edges occurring in 1 sec using the timer to time 1 sec and the counter to count events

Pulse Accumulator • 5 relevant control registers (p. 204 transparency) • PortA itself; PA7 pin confiscated for accumulator • TMSK2/TFLG2 (same as 16-bit timer) – interrupt arms and flags • PACTL • DDRA7 for direction of PA7 • PAEN to enable PA system • PAMOD,PAEDGE to select operation mode 0 0 event counting PA7 falling edge 0 1 event counting PA7 rising edge 1 0 gated time accumulated on PA7 high 1 1 gated time accumulated on PA7 low • PACNT the 8-bit count

Software Interrupts, or Traps • on 6811/12: single swi for software interrupt • on 680x0: 16 trap #n • on x86: 256 int #n • Traps like subroutines, except trap address bound dynamically, not statically at assemble/compile time • Uses: • OS system calls (so your code doesn’t know/care exactly where OS routines are • Breakpoints for debugging • 6811/12: Trap vector “table” – i.e. table of pointers to trap handlers – contains 1 entry; obviously more on other systems!

swi • Push ALL registers on stack, including PC and CC • I bit is set in CC after pushing CC • Load trap vector (stored in $FFF6-$FFF7) in PC, perform desired function (arbitrary assembly code) • Traps redirected in Axiom ROM to RAM • rti passes control back to interrupted program • pops all registers including PC and CC; restores I bit in process

Uses of swi • A simple OS might be nothing more than a loader program and a series of useful functions designed as traps • Breakpoints: replace desired break location with swi; trap handler takes control • interact with user • print out register values • execute desired code or alternate code • return back to run mode

Hardware Interrupts • initiated by events asynchronous and external to the CPU • exception: exceptions! • automated transfer of software execution to routine appropriate to specific interrupt occurring • each (possibly recursive) interrupt invokes a new thread of control; on return the interrupted thread must be unperturbed

Basic Interrupt Processing • Interrupts typically must be armed and/or enabled • 6811: global IE bit plus arm for each interrupt • Interrupt is asserted (external or internal causes) • priority arbitrated if more than one • Complete current instruction • remember – not pipelined, so easy to “drain” • Suspend current program • push all registers including PC, CC on stack • Load PC with vector • Disable further interrupts • RTI when done to restore registers and I bit

Hardware interrupt list • From Freescale docs • 25 distinct interrupts or traps; 21 vectors

Hardware interrupt list • From Freescale docs • 25 distinct interrupts or traps; 21 vectors 1 vector for 5 interrupts?

Vector redirection • On our boards, all vectors are in ROM space (FFxx) • So where do they point? How do we get them to point to our handlers? • Thanks to Buffalo, ROM vectors point to RAM addresses, last page in Axiom hardware manual $00C4-$00C6 SCI $00C7-$00C9 SPI $00CA-$00CC Pulse Accumulator Input Edge Etc. 3 bytes per vector. Why?

Redirects $00C4: JMP <SCI Handler> in EEPROM $00C7: JMP <SPI Handler> in EEPROM $00CA: JMP <PA Input Edge Handler> … JMP opcode is 7E Code you will have to load into RAM as data! So in your code: to load SCI handler ldaa #$7E staa $00DF ldx #OC1_Han OC1_Han is in your code stx $00E0 Also explains the $0100 approach to using RAM: these redirects use $00C4-$00FF

Interrupt Priorities • For simultaneous requests • Most NMIs are reset related Freescale docs