Visual Tool for Congestion Estimation and Localization in FPGA Design

This paper presents a visual tool developed for estimating and localizing congestion in FPGAs, aimed at improving interconnect prediction. The study explores different congestion localization heuristics before and after placement, addressing the challenges of fixed routing architectures in FPGA design. It emphasizes the importance of accurate congestion estimation to balance interconnect resources effectively while minimizing wastage. Key results demonstrate that augmenting existing CAD tools can enhance routability and performance, setting a foundation for future work in FPGA architecture optimization.

Visual Tool for Congestion Estimation and Localization in FPGA Design

E N D

Presentation Transcript

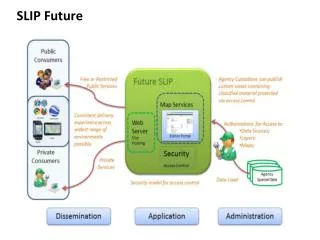

SLIP 2007 Congestion Estimation and Localization in FPGAs:A Visual Tool for Interconnect PredictionDavid YeagerDarius ChiuGuy LemieuxThe University of British ColumbiaDepartment of Electrical and Compute Engineering

SLIP 2007 Outline • Motivations for congestion localization heuristics. • Exploring heuristics • Post-placement • Pre-placement • Results • Future Work

SLIP 2007 FPGAs: FIXED Routing Architecture • Fixed Channel Width. • Over 80% of resources devoted to interconnect. • Comprised of repeated tiles. • Routing resources identical throughout. • Can potentially have enough logic resources, not enough routing resources for a design.

Architecture design involves retargetable CAD flow. • Cover large amount of customer benchmarks. • Routing resources accommodate majority of customer designs that fit in FPGA's logic resources. • Requires excessive amount of fixed interconnect. SLIP 2007 FPGA Routing Architecture Design • FPGA Architecture design involves retargetable CAD flow. • Explore different amounts of routing resources. • Select routing that performs best across all circuits. • Less fixed routing = higher density, performance. • Less fixed routing = more unroutable designs. • More fixed routing = more wastage. • Can use 100% of logic resource. • Can never use 100% of routing resources. • Results in excess programmable interconnect. • Congestion aware CAD improves routability. • Allows architects to get away with less excess • programmable interconnect.

SLIP 2007 FPGA vs ASIC Congestion Impact • Two CAD flows. • All results are equal EXCEPT... • Only one produces evenly distributed interconnect. • ASIC world => No major advantage. • FPGA world => Smaller channel width. • Allows for denser FPGA architecture. • Reduces interconnect wastage. • Locating congestion can help with this balancing.

SLIP 2007 Balanced Routing: Denser FPGA Channel Width = 7 Channel Width = 3

SLIP 2007 Further Motivations for Congestion Localization • High quality congestion estimation can be slow. • May not be realistic to constantly update with every move. • Localization can give different weights to different nets, CLBs, LUTs. • Update weights during intervals. • Example application: SA optimization, Un/Dopack.

SLIP 2007 Motivations for accurate congestion estimation: Un/DoPack yes channel width constraint met? start with netlist cluster place route no success yes yes available area left? channel width constraint met? congestion calculator depopulated clustering incremental place incremental route no no failure

SLIP 2007 Motivations: Un/DoPack start with netlist cluster place yes channel width constraint met? congestion calculator route no success yes available area left? depopulated clustering incremental place congestion calculator no yes channel width constraint met? route failure no

SLIP 2007 Motivations: Un/DoPack start with netlist cluster yes channel width constraint met? place congestion calculator route no success yes yes available area left? congestion calculator depopulated clustering no yes channel width constraint met? failure place route no

SLIP 2007 Motivations for accurate congestion localization: Un/DoPack • Identify regions to add white space

SLIP 2007 Congestion Localization Measurement • Requirements: Applicable before and after placement, can integrate into Un/Dopack, can be easily displayed visually. • Solution: Assign a congestion value to each CLB. • Allows for localization before and after placement. • Assigning to specific routing resources not practical before placement. • Quality Measurement: Perform full place and route. Real congestion = Max tracks on each side of CLB. Compare to estimate.

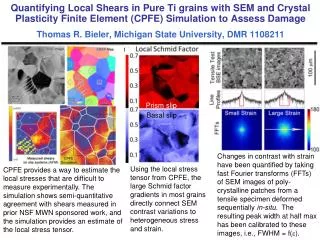

SLIP 2007 Quality Measurement: Fidelity VS Accuracy • Previous work reports accuracy of estimate to actual peak channel widths. • Does not report localization quality, or fidelity. • Congestion estimation requires both accuracy and fidelity. • Accuracy well studied. Therefore fidelity is the focus of this work. • Fidelity can always be scaled to an accuracy heuristic. • Good localization required to balance congestion. • Fidelity = FPGA centric measurement. Higher Fidelity Higher Accuracy Actual congestion Poor Localization Good Localization from router

SLIP 2007 Measuring Fidelity • Linearly scale actual and real congestion maps so that min and max congestion of both maps are equal. • Subtract difference between each CLB's congestion estimate and actual CLB's congestion value after place and route. • % Error = Avg of absolute value of the differences / peak CLB congestion. • Average absolute normalized error. • M rows, M columns. E = Estimate, R = Real :

Exploring heuristics: Local Rent Exponent SLIP 2007 • Plot average cuts per partition size • line of best fit: log T = p●log(G) + log(t) • T =aGP • p = Rent exponent. We will use this as our congestion value. Window Size = 5 log (# of cuts) log (# of CLBs)

SLIP 2007 Exploring heuristics: Local Rent Exponent • Benefit: • Characterizes wire length distribution. • Downsides: • Requires a lot of data points. • Better for characterizing entire circuits. • Smaller window subject to anomylies. • Larger window loses locality of estimation. • Rate of change of cuts, not absolute value.

SLIP 2007 Exploring heuristics: Net cuts per region • Rent exponent captures rate of change of cuts => wire length distribution. • Absolute number of cuts may be better for locality. • Example: region size of 3x3. Count number of nets crossing this boundary.

SLIP 2007 Post Processing Heuristic #1: Cartesian Blending Blend Step 0 A0 B0 C0 D0 E0 F0 G0 H0 I0 J0 K0 L0 F1 = (1-α)*F0 + α*(E0 + B0 + G0 + J0)/4G1 = (1-α)*G0 + α*(F0 + C0 + H0 + K0)/4

SLIP 2007 Post Processing Heuristic #1: Cartesian Blending Blend Step 1 A1 B1 C1 D1 E1 F1 G1 H1 I1 J1 K1 L1 F2 = (1-α)*F1 + α*(E1 + B1 + G1 + J1)/4G2 = (1-α)*G1 + α*(F1 + C1 + H1 + K1)/4

SLIP 2007 Exploring heuristics: Bounding Box Overlap • Assign CLB value equal to number of bounding boxes it resides in. • Zhuo et al. use this during every SA swap in VPR's placer, yielding avg of 7.1% channel width reduction.

SLIP 2007 Exploring heuristics: Wire Length Per Area • Expected wire-length of net = ½ perimeter bounding box

Exploring heuristics: Bounding Box SLIP 2007 • Probability of net routed at any given point in bounding box = expected length / bounding box area.

SLIP 2007 Exploring heuristics: Wire Length Per Area • ½ perimeter bounding box not realistic for high fan-out nets. extra pin factor = min(BBWidth, BBHeight)*max(0,num_pins – 3) expected wire length = 1/2BB + (extra pin factor)*α probability of wire = expected wire length / area

SLIP 2007 Exploring heuristics: Bounding Box • Blending helps spread probability distribution. • Probability outside bounding box > 0. p(wire) > 0 p(wire) = 0