Module 1: Introduction Topic 3: Interconnect Technology

Module 1: Introduction Topic 3: Interconnect Technology. OGI EE564 Howard Heck . Where Are We?. Introduction Overview Trends & Challenges Interconnect Technology Transmission Line Basics Analysis Tools Metrics & Methodology Advanced Transmission Lines Multi-Gb/s Signaling

Module 1: Introduction Topic 3: Interconnect Technology

E N D

Presentation Transcript

Module 1: IntroductionTopic 3: Interconnect Technology OGI EE564 Howard Heck Section 1.3

Where Are We? • Introduction • Overview • Trends & Challenges • Interconnect Technology • Transmission Line Basics • Analysis Tools • Metrics & Methodology • Advanced Transmission Lines • Multi-Gb/s Signaling • Special Topics Section 1.3

Contents • Component Packaging • Passive Components • Connectors • Printed Circuit Boards Section 1.3

Overview (Chip + Pkg) PCB (add-in card) Connector Components PCB (Motherboard) Source: Intel Corp. Section 1.3

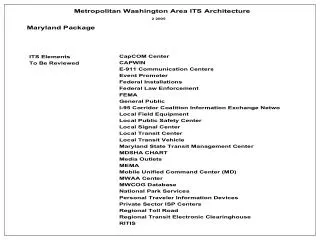

Overview – SOA Desktop Motherboard Graphics Connector Chipset Microprocessor Memory Slots Section 1.3

Overview – SOA Desktop Motherboard Memory Connectors Chipset Graphics Connector Microprocessor X48 chipset motherboard Section 1.3

Component Packaging • Packages house the silicon chips. They provide: • Mechanical support • Heat removal • Environmental protection • Electrical signal & power connections (chip to PCB). Heat Spreader Silicon Package PCB Soldered Connections Section 1.3

Component Packaging Section 1.3

Component Packaging Source: Intel Corp. Section 1.3

Example: Flip Chip Pinned Grid Array Top Bottom Cross-section Section 1.3

Medium Speed Package Electrical Models Bond Wire Trace Pin / Land L R L R bw bw pin pin Die Board t Z , 0 d R , L , C tb tb tb Tie Bar Source: Packaging Databook, Intel Corp Today’s speeds demand that we use fully coupled 3D package models. Section 1.3

Passive Components Resistors • Uses: termination for interconnect, pull up/down for static features • Variability: 5%, 2%, 1% • Chip resistors – 1 resistor per component • R-Packs – up to 4 resistors per small outline component • Resistor networks – more resistors per component • Lead inductance and package crosstalk can be important effects for high frequency applications. Capacitors • Variability: 20%, 10% • Chip capacitors – used for high frequency (local) decoupling of power suppliers • Tantalum capacitors – used for bulk decoupling • At high frequencies, resistance and inductance of the packages must be included in the models. Section 1.3

Sockets & Connectors • Sockets connect packages to PCBs. • Connectors connect PCBs to PCBs. • Connection is mechanical between two metal surfaces. DIMM connector LGA775 Socket PCI® Express Section 1.3

Socket/Connector Electrical Models t R Z , con 0con dcon • These are simple models. Coupled models are frequently used for high performance applications. Today’s speeds demand that we use fully coupled 3D connector models. Section 1.3

Printed Circuit Boards • Function: provide electrical signal connections between components & deliver power to the components. • Material Set: • Construction: • Typically 4 to 6 layers (always an even number). • 4 layer board: 2 signal, 2 power ($0.09/in2) • 6 layer board: 4 signal, 2 power ($0.18-$0.24/in2) • Higher layer counts are available at higher cost. Section 1.3

PCB Construction Signal Trace Surface Mount Pad Via Land Power Plane Laminate (Dielectric) Solder Mask Via Barrel Solder Mask Signal Trace Laminate (Resin) Power Plane Laminate (Glass) Section 1.3

PCB Signal Layer f 0.024" D 2 f 0.012" D 1 0.005" W 0.006" S 2 G 0.050" 0.005" S 1 Section 1.3

PCB Vias • Vias make layer-layer connections by drilling holes and filling them with conductor material (copper). • They are used in chips, package, and boards. Heat Spreader Silicon Package PCB Soldered Connections Section 1.3

PCB Design Goals • Function: All signals connected • Performance: Maximum operating frequency • Cost • Minimized technology requirements • Layer count • Board size • Relaxed width & spacing • Relaxed via size • Design for manufacturability • Component selection • Component placement • Trade routing Section 1.3

Summary • Package electrical parameters are typically modeled with lumped circuit elements and transmission lines. • We will examine the effects of lumped elements later, and will account for them in our design project. We will also consider when transmission line models are required. • For high volume PCs, system designers use pervasive, low cost PCB solutions: • FR-4 material set • 4 layer boards • 5/5 or 6/6 mil trace/space wiring • 4 boards per panel for motherboards • PCBs are used for motherboards, add-in cards, and CPU packages. • PCBs provide interconnect for high speed buses operating as high as 400 MHz/800 MT/s and beyond. Section 1.3

References • Intel Packaging Databook, Intel Corporation, 2002, http://developer.intel.com/design/packtech/packbook.htm. • Component Types Used for SMT, IBM Microelectronics Division, January 1994. • Surface Mount Design and Land Pattern Standard, IPC-SM-782, IPC, Revision A – August 1993. • R.R. Tummala, E.J. Rymaszewski (ed.),Microelectronics Packaging Handbook, Van Nostrand Reinhold, New York, 1989. Section 1.3

Appendix: More Packages Celeron® Processor Package Celeron® Processor Cartridge Pentium® Processor w/ MMX™ Package 850 Chipset Package Section 1.3

Appendix: More Connectors PCI ISA SLOT1 Memory DIMM AGP Section 1.3

Appendix: CPU Sockets PGA370 Section 1.3