**Hardware and Firmware Progress Update**

70 likes | 174 Views

Detailed progress update on AFE IIt and VLSB memory banks, charge and time data storage, and data flow control. Includes developments in firmware, hardware modifications, and board preparation for production cryostats.

**Hardware and Firmware Progress Update**

E N D

Presentation Transcript

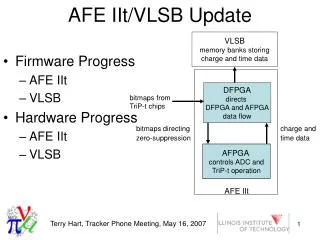

AFE IIt/VLSB Update VLSB memory banks storing charge and time data • Firmware Progress • AFE IIt • VLSB • Hardware Progress • AFE IIt • VLSB DFPGA directs DFPGA and AFPGA data flow bitmaps from TriP-t chips bitmaps directing zero-suppression charge and time data AFPGA controls ADC and TriP-t operation AFE IIt Terry Hart, Tracker Phone Meeting, May 16, 2007

AFE IIt Firmware • Progress since April phone meeting • Worked out, coded, and simulated operation of bidirectional data bus • Protocol of data transfers on bidirectional bus • Operation of event buffer and pipeline • Successful test of data bus at 53.104 MHz • Worked out data format and operation modes • Current plans • Working out protocol for keeping data streams within AFE IIt boards synchronized Terry Hart, Tracker Phone Meeting, May 16, 2007

VLSB Firmware • Direct Memory Access Block Transfers • Code found which accomplished this • Fast Clear of VLSB memory banks • Should be done with simple code modifications • Advance memory address only when receiving data (not when receiving zeros) • Initial code written which needs to be tested • May require Aldec design tool Terry Hart, Tracker Phone Meeting, May 16, 2007

AFE IIt Hardware • Matching boards to production cryostats • Currently, 8 boards almost ready for 2 cryostats • Malcolm wrote document listing necessary hardware modifications and firmware uploads • Hardware modifications include soldering surface mount components • Kwame Bowie currently uploads firmware as boards become ready. • Spare boards to be sent to RAL for repairs • Accounting of boards at FNAL, RAL, and Imperial made. Terry Hart, Tracker Phone Meeting, May 16, 2007

VLSB Hardware • Determined that VLSB boards don’t need to be redesigned for MICE modifications • Have 11 boards, need about 13 more • Existing MOU needs to be followed up to make VLSB modules Terry Hart, Tracker Phone Meeting, May 16, 2007

Jan Feb Mar Apr May Jun Jul Aug Sep Oct Nov Dec TriP-t/ADC Control Firmware Hardware tests DFPGA/AFPGA I/O Bus Board test at 53.104 MHz Board test at 55 MHz Simulations at different frequencies Data transfer protocol AFPGA Firmware Write firmware controlling bitmap transfers Test pipeline/buffer operation Test mode development DFPGA Firmware Make 4-level trigger buffer Data format Event aggregation VLSB Firmware Data block transfer Fast clear of memory banks Suppress writing zeros to memory Done Done Done

Jan Feb Mar Apr May Jun Jul Aug Sep Oct Nov Dec TriP-t/ADC Control Firmware Hardware tests DFPGA/AFPGA I/O Bus Board test at 53.104 MHz Board test at 55 MHz Simulations at different frequencies Data transfer protocol AFPGA Firmware Write firmware controlling bitmap transfers Test pipeline/buffer operation Test mode development DFPGA Firmware Make 4-level trigger buffer Data format VLSB Firmware Event aggregation (VLSB) Data block transfer Fast clear of memory banks Suppress writing zeros to memory VLSB Board Manufacture (13 boards) AFE IIt Board Preparation Repairs for MICE Firmware and hardware modifications Board characterization in cryostats Ship cryos/boards to RAL Done Done Done Conservative simulations indicate this is marginal Conservative simulations this is marginal Done Done Standalone routine written Feedback loop testing previous version Done, sort of Low to middle priority Done Should be quick, how to tell when clear is done Initial code written, needs to be tested Follow up on existing MOU Ongoing Ongoing Ongoing