Optimization of Sequential Networks: Step in Synthesis

190 likes | 245 Views

This article focuses on minimizing states for completely specified and incompletely specified sequential machines by reducing flow tables to their minimum state representation. Learn about techniques such as state assignment, transition table optimization, and flip-flop selection. Discover how to merge equivalent states to achieve the minimum number of states using partition and array techniques.

Optimization of Sequential Networks: Step in Synthesis

E N D

Presentation Transcript

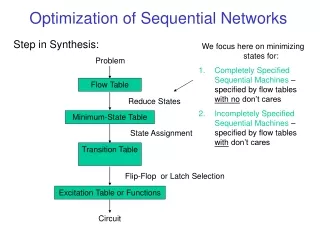

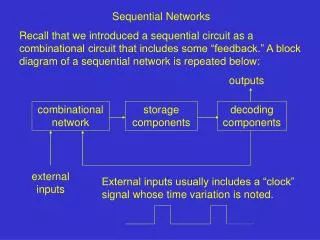

Optimization of Sequential Networks • Step in Synthesis: • We focus here on minimizing states for: • Completely Specified Sequential Machines – specified by flow tables with no don’t cares • Incompletely Specified Sequential Machines – specified by flow tables with don’t cares Problem Flow Table Reduce States Minimum-State Table State Assignment Transition Table Flip-Flop or Latch Selection Excitation Table or Functions Circuit

State Reduction Goal • Given a flow table, to find an indistinguishable, minimum-state flow table. • Note: this leads to a circuit with fewest possible memory elements & usually a minimum cost (but not always) • Indistinguishable Flow Tables - flow tables that specify identical output sequences for the same input sequence. • Inaccessible States – states not reached from initial state or from desired pattern • We want to eliminate inaccessible states by state reduction or by making them accessible. • We assume this is done before other state reduction techniques are employed.

Table Reduction forCompletely Specified Networks Consider two flow tables: Table T Table T* If the same input sequence is applied to T or T*, they produce the same output sequences Example: for sequence x = 011, z(T,A)=101, z(T*,E)=101

Distinguishability Two states of a FSM si and sj are distinguishable if they produce different output sequences for the same input sequence. Such an input sequence is a distinguishing sequence of (si, sj) Two states of a FSM si and sj are equivalent or indistinguishable if they produce the same output sequences for the same input sequence and are members of an indistinguishable class. If there is a distinguishing sequence with length k for (si, sj), the (si, sj) is k-distinguishable Goal: to merge all equivalent states to obtain the minimum number of states.

Partition and Array Techniques to Produce Minimum-State Tables • Partition Test • Steps: • Class States by output only A[Q0Q2Q4] B[Q1Q5Q6] C[Q3]

Partition Test • Steps: • Check Next States within classes, if necessary further subclass A[Q0Q2Q4] B[Q1Q6] BD[Q5] C[Q3]

Partition Test Steps: 3. Minimum-State Table is set of indistinguishable classes. A[Q0Q2Q4] B[Q1Q6] BD[Q5] C[Q3]

Array Technique • Steps: • Form Pair Chart with ½(S)(S-1) entries. Place X in cells that correspond to state pairs having different outputs. 2. Each remaining pair examined, place asterisk in cells with identical next state entries. Place pairs of states that must be indistinguishable in order that pair represented by cell be indistinguishable Q1 X Q2 X Q2Q4 X X X Q3 Q0Q2Q1Q6 Q1Q6Q0Q4 X X Q4 Q2Q3Q0Q2 X X X X Q5 Q2Q4Q0Q2 Q6 X X X X Q3Q4 Q0 Q1 Q2 Q3 Q4 Q5

Array Technique 3. Make successive passes through array Xing out cells having pair entries that are distinguishable (marked by X elsewhere in Table) Q1 X Q2 X Q2Q4 X X X Q3 Q0Q2Q1Q6 Q1Q6Q0Q4 X X Q4 Q2Q3Q0Q2 X X X X Q5 Q2Q4Q0Q2 Q6 X X X X Q3Q4 Q0 Q1 Q2 Q3 Q4 Q5 Result: [Q0Q2Q4] [Q1Q6] ] [Q3] [Q5]

Optimization of Incompletely Specified Machines • Some definitions: • Two states are I-Equivalent IFF • Outputs are identical, if specified • Matching d-outputs occur • Matching unspecified next states occur or specified next states must be equivalent. • Two states are Compatible IFF • Outputs are identical, if specified • Compatible next-states occur, if both are specified. Maximal Compatible Classes - classes that are not subsets of any other compatibility class.

Optimization of Incompletely Specified Machines Flow Table I-Equivalent States Removed Compatible State Pair Chart Maximal Compatibility Classes Minimum-State Table

Optimization of Incompletely Specified Machines • Steps in finding Reduced Table: • Remove I-Equivalence states • Find Maximal Compatibility Classes • Form Flow Table in which each state corresponds to a maximal compatibility class subject to satisfying the closure property and all states of the original table are represented, that is satisfying the covering property.

Optimization of Incompletely Specified Machines – Array Technique Example: B X C AD * BE AE DE D AB.BC CE BC BC E A B C D Compatibility State Set: [AC], [AD], [CD], [ACD], [BC], [BE], [ED] Maximal compatibility classes

Optimization of Incompletely Specified Machines – Merger Graph Complete Subgraph Example: A B (DE) (BC) E (AE) (AD) (BC) (BE) (BC) (AB) D (DE) C Compatibility State Set: [AC], [AD], [CD], [ACD], [BC], [BE], [ED] Maximal compatibility classes

State Compatibility Graph • State Compatibility Graph is a directed graph satisfying the conditions: • Each node corresponds to a compatible state set. • When a state set implies another state set S, attach OR directed edges from the nodes corresponding to the original state set to the node corresponding to the state sets containing S. • When a state set implies two or more state sets: S0, …., Sk-1, Sk, Attach AND directed edges from the node corresponding to the original state set to the nodes that correspond to S0, …., Sk-1, Sk

Finding Minimum Number of States Using State Compatibility Graph • Must Satisfy Two Conditions: • Covering Property – Each state of the FSM is contained by at least one compatible set V • Closure Property: If viV, then ViV, where Vi is the set of implied compatible sets. Visatisfies the following condition: for the OR directed edges that emerge from vi, Vi contains the nodes for at least one edge. For the AND directed edges that emerge from vi, Vicontains the nodes for all the AND directed edges.

Addressing the Closure Property B (DE) (BC) E (AE) (AD) (BC) (BE) (BC) (AB) D (DE) V1 : [BE] V2 : [AD] V3 : [CD] V4 : [BC] V5 : [ACD] V6 : [DE] V7 : [AC] V8 : [A] V9 : [B] V10 : [C] V11 : [D] V12 : [E] V7 V8 V9 V10 V11 V12 V3 V1 V6 AND V5 V2 OR V4

Optimization Example Covering Property State A: v2 + v5 + v7 + v8 = 1 State B: v1 + v4 + v9 = 1 State C: v3 + v4 + v5 + v7 + v10 = 1 State D: v2 + v3 + v5 + v6 + v11 = 1 State E: v1 + v6 + v12 = 1

Closure Property Example From the state compatibility graph v1v4 , so v1 + v4 = 1 v2v1 , so v2 + v1 = 1 v3v6 , so v3 + v6 = 1 v4 (v2 + v5), so v4 + v2 + v5 = 1 v5v1v6, so (v5 + v1)(v5 + v6)= 1 v6v4 , so v6 + v4 = 1 AND of all conditions gives solution of minimum weight