The Simplified Instructional Computer (SIC)

410 likes | 867 Views

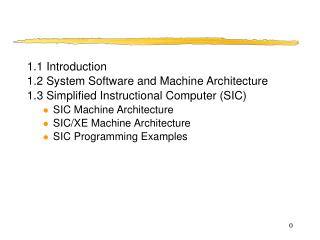

The Simplified Instructional Computer (SIC). Hsiang-Fu Yu National Taipei University of Education. Outline. The Simplified Instructional Computer (SIC) (Sec. 1.3) Traditional CISC Machines (Sec. 1.4) RISC Machines (Sec. 1.5). SIC Architecture. Two versions SIC

The Simplified Instructional Computer (SIC)

E N D

Presentation Transcript

The Simplified Instructional Computer (SIC) Hsiang-Fu Yu National Taipei University of Education

Outline • The Simplified Instructional Computer (SIC) (Sec. 1.3) • Traditional CISC Machines (Sec. 1.4) • RISC Machines (Sec. 1.5)

SIC Architecture • Two versions • SIC • SIC/XE (extra equipments or extra expensive) • SIC program can be executed on SIC/XE. (upward compatible) • Memory consists of 8-bit bytes. 3 consecutive bytes form a word (24 bits) • There are 215 (32K) bytes in the memory

Registers • There are 5 registers • Each is 24 bits in length

Data Format • Integer • 24-bit binary numbers • 2’s complement representation is used for negative numbers • Character • store using their 8-bit ASCII codes • There is no floating-point hardware on SIC

Instruction Format • All machine instructions on SIC has the following 24-bit format • Only two addressing modes X is used to indicate indexed-addressing mode

Instruction Set • Load and store registers • LDA, LDX, STA, STX • Integer arithmetic • ADD, SUB, MUL, DIV, all involve register A and a word in memory • Comparison • COMP, involve register A and a word in memory • set a condition code CC to indicate the compare result

Instruction Set (cont.) • Conditional jump • JLE, JEQ, JGT, etc. • test the setting of CC and jump accordingly • Subroutine linkage • JSUB • jump to the subroutine, placing the return address in register L • RSUB • return by jumping to the address contained in register L

Input and Output • One byte at a time to or from the rightmost 8 bits of register A • Each device has a unique 8-bit ID code • Test device (TD) • test if a device is ready to send or receive a byte of data • Read data (RD) • read a byte from the device to register A • Write data (WD) • write a byte from register A to the device

SIC/XE Architecture • Memory size • 1 megabytes (220 bytes) • An address (20 bits) cannot be fitted into a 15-bit field as in SIC Standard • Lead to changes in instruction formats and addressing modes • Extra registers

Data Format • The same as that of SIC • There is a floating-point data type with the following format • fraction is between 0 and 1 • exponent is between 0 and 2047 • Zero is presented as all 0 (-1)s*fraction*2(exponent-1024)

Instruction Formats Formats 1 and 2 do not reference memory at all Format 1 (1 byte) Format 2 (2 bytes) Format 3 (3 bytes) e = 0 Format 4 (4 bytes) e = 1 Bit e distinguishes between formats 3 and 4 Large memory extends addressing capacity

Addressing Modes b=1, p=0, TA=(B)+disp (0disp 4095) b=0, p=1, TA=(PC)+disp (-2048disp 2047)

Addressing Modes (cont.) Format 3: b=0, p=0, TA=disp (0disp 4095) Format 4: b=0, p=0, TA=addr

Addressing Modes (cont.) • Indexed addressing mode TA=(X)+disp TA=(X)+disp+(PC) TA=(X)+disp+(B)

Addressing Modes (cont.) For formats 3 and 4: • Immediate addressing mode (n = 0, i =1) • The target address is used as the operand • Indirect addressing mode (n = 1, i = 0) • The word at the location given by the target address is fetched • The value contained in this word is then used as the address of the operand value • Simple addressing mode • The target address is taken as the location of the operand • (n = 1, i = 1) used by SIC/XE • (n = 0, i = 0) used by SIC Indexed addressing cannot be used with immediate or indirect modes.

4: Format 4 instruction D: Direct-addressing instruction , i.e., non-relative addressing , b = 0 and p = 0 A: Assembler selects either program-counter relative or base- relative mode S: Compatible with SIC

PC-relative simple addressing: (PC) + disp Base-relative indexed simple addressing: (B) + disp + (X) PC-relative indirect addressing: (PC) + disp Immediate addressing: disp SIC simple addressing: b/p/e + disp Simple addressing: addr All of these instructions are LDA.

Instruction Set • LDB and STB • Floating-point operations • ADDF, SUBF, MULF, DIVF • Register move • RMO • Register-to-register operations • ADDR, SUBR, MULR, DIVR • Supervisor call for generating system calls into the operating system • SVC • I/O channel operation similar to DMA • SIO: start, TIO: test, HIO: halt

Complete Instruction Set P: privileged instruction X: available only on XE F: floating- point Instruction C: condition code CC set to indicate result of operation

SIC Programming Examples Immediate addressing makes the program run faster because it need not fetch five from the memory.

SIC Programming Example (Fig. 1.3a) BETA <- (ALPHA + INCR - 1) DELTA <- (GAMMA + INCR - 1)

SIC/XE Programming Example (Fig. 1.3b) This program will execute faster because it need not load INCR from memory each time when INCR is needed.

SIC Programming Example (Fig. 1.4a) • Looping and indexing: copy one string to another

SIC/XE Programming Example (Fig. 1.4b) This program will execute faster because TIXR need not compare the index value to a memory variable.

SIC Programming Example (Fig. 1.5a) Gamma [] <- Alpha [] + Beta []

SIC/XE Programming Example (Fig. 1.5b) This program will execute faster because it uses register-to-register add to reduce memory accesses.

SIC Programming Example (Fig. 1.7a) Read 100 words into the record buffer

SIC/XE Programming Example (Fig. 1.7b) Use TIXR makes this program run faster

Reduced Instruction Set Computer (RISC) Machines • RISC system • Instruction • Standard, fixed instruction format • Single-cycle execution of most instructions • Memory access is available only for load and store instruction • Other instructions are register-to-register operations • A small number of machine instructions, and instruction format • A large number of general-purpose registers • A small number of addressing modes

Some RISC machines • SPARC family • PowerPC family • Cray T3E • ARM • MIPS

Traditional (CISC) Machines • Complex Instruction Set Computers (CISC) • Complicated instruction set • Different instruction formats and lengths • Many different addressing modes • Examples • VAX • Intel x86 Processors