Timing Bug in CSC Digis

60 likes | 84 Views

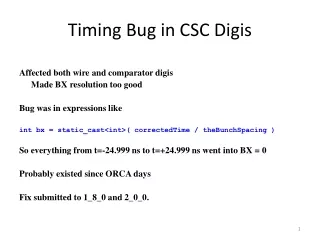

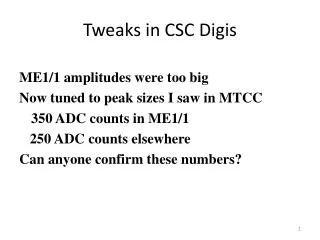

A bug in CSC Digis affected both wire and comparator digis, causing incorrect BX resolution due to expressions involving time calculation. The bug, potentially existing since the ORCA days, has been addressed in versions 1.8.0 and 2.0.0. The effects on triggering are currently under investigation. New TF logic will be implemented in 1.8.0 for improved accuracy. The adjustment now centers digis on tbin=6, a change from previously tuning towards later BXs.

Timing Bug in CSC Digis

E N D

Presentation Transcript

Timing Bug in CSC Digis Affected both wire and comparator digis Made BX resolution too good Bug was in expressions like int bx = static_cast<int>( correctedTime / theBunchSpacing ) So everything from t=-24.999 ns to t=+24.999 ns went into BX = 0 Probably existed since ORCA days Fix submitted to 1_8_0 and 2_0_0.

Effects on Triggering • Under investigation now • In earlier TF, a digi 1 BX early could ruin global muon trigger! • New TF logic will be in 1_8_0 • Now we tune timing to center digis on tbin=6 • Before, we had to err towards later BX.