EE 587 SoC Design & Test

EE 587 SoC Design & Test. Partha Pande School of EECS Washington State University pande@eecs.wsu.edu. Power & Low Power Design Physical Design Methodologies. Clocked Logic Family. Domino circuits only implement noninverting logic High activity Better suited for large fanin gates

EE 587 SoC Design & Test

E N D

Presentation Transcript

EE 587SoC Design & Test Partha Pande School of EECS Washington State University pande@eecs.wsu.edu

Power & Low Power Design Physical Design Methodologies

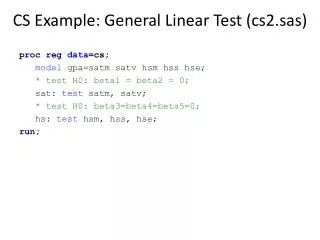

Clocked Logic Family • Domino circuits only implement noninverting logic • High activity • Better suited for large fanin gates • Ref: Dinesh Somasekhar and Kaushik Roy, “Differential Current Switch Logic: A Low Power DCVS Logic Family”, IEEE Journal of Solid-state Circuits, Vol. 31, No. 7, July 1996

Clocked CVSL • The PMOS precharge transistors to pull the inverter inputs high during the low phase of the clock • Outputs are evaluated in the high phase of the clock • The weak PMOS feedback prevents deterioration of the high level at the inverter inputs

SSDL • Sample set differential logic (SSDL) • Complementary outputs are driven using an inverter loop • Senses the differential levels set up by the NMOS tree

ECDL • Enabled/disabled CMOS differential Logic • Avoids high power consumption of SSDL • Pre charge low

Differential Current Switch Logic (DCSL) • DCSL belongs to the class of clocked differential cascode voltage switch logic circuits • It is a generic methodology which is applied to clocked DCVS gates to reduce internal node voltage swings

DCSL1 • Differential current switch logic (DCSL) • The low going transition of Q disconnects the NMOS tree from Q_b by progressively cutting off transistor T8 • This limits the charge up of the internal nodes in the NMOS tree • SPICE simulations show that the internal node voltage swings for DCSL are of the order of 1volt (supply voltage 5 v)

Skewed CMOS • Fully complementary static logic • The sizes of the PMOS and NMOS transistors are adjusted to enable one of the transitions to be faster than the other • Noise tolerance of skewed logic is better than the dynamic circuits • Ref: A. Solomatnikov et. al. “Skewed CMOS: Noise-Tolerant High-Performance Low-Power Static Circuit Family”, IEEE Transactions on VLSI, Vol. 10, No. 4, August 2002

Skewed CMOS • Comparable to Domino, with a better noise margin • Better for low voltage, low power applications • Fast high-to-low transition gate should be followed by fast low-to-high transition gate

Multiple Threshold Voltage • Threshold Voltage is one of the most important parameters for device and circuit design • For the active mode low Vth is preferred because of the higher performance • For standby mode high Vth is useful for reduction of leakage power

Self-Adjusting Threshold Voltage Scheme • A leakage sensor senses a representative MOSFET and generates a control signal to self-sub-bias circuit • Consider an nmos transistor • When the leakage current is higher than a certain value, the SSB will be triggered and will reduce the substrate bias of all the other nmos transistors, which in turn will increase the threshold voltage and reduce leakage current

MTCMOS • In active mode, low-VT MOSFET’s achieve high speed. • In standby mode when St'by signal is high, high-VT MOSFET’s in series to normal logic circuits cut off leakage current.

Issues in MTCMOS • Virtual ground not actual ground (lose some noise margin) • Can increase width of sleep transistor to reduce voltage at virtual ground but it will also increase subthreshold leakage and area of sleep transistor

Variable Threshold-CMOS • Threshold voltage of both devices are increased by adjusting the body-bias voltage in order to reduce subthreshold leakage current in standby mode • Requires twin-tub technology so that substrates of individual devices can be adjusted

Dynamic Voltage Scaling • In dynamic supply voltage scaling, the logic chip is designed to deliver maximum performance at the highest supply voltage • When the performance demand is low, the chip is operated at lower voltage, delivering lower performance but with substantial (quadratic) reduction in power • The logic chip could also detect the performance demand and adjust frequency and supply voltage accordingly

Static Supply Voltage Reduction • In static supply voltage reduction method, multiple supply voltages are used • Higher supply voltage is used for performance critical logic, which runs at higher speeds, and consumes higher power.

Summary • Major concern today is leakage power. • Need to exploit cooperation among levels: • Software, architecture, algorithm, system, EDA, • circuit, technology, assembly • Power-aware electronics opens up vast new applications and market.