Concurrent Test Generation

Vishwani D. Agrawal, vagrawal@eng.auburn.edu Alok S. Doshi, dosias@auburn.edu. Concurrent Test Generation. Auburn University, Department of Electrical and Computer Engineering Auburn, AL 36849, USA For more details, see http://www.eng.auburn.edu/~vagrawal. Problem Statement.

Concurrent Test Generation

E N D

Presentation Transcript

Vishwani D. Agrawal, vagrawal@eng.auburn.edu Alok S. Doshi, dosias@auburn.edu Concurrent Test Generation Auburn University, Department of Electrical and Computer Engineering Auburn, AL 36849, USA For more details, see http://www.eng.auburn.edu/~vagrawal Texas Instruments (India)

Problem Statement • To find the smallest test set to detect all single stuck-at faults in a combinational circuit. • An existing solution: • Group faults into fault sets using fault independence • Generate concurrent tests for each group • Contribution of this paper: Devise a simulation-based implementation for this solution. Texas Instruments (India)

Outline • Introduction • Simulation-based Independence Fault Collapsing • Simulation-based Concurrent Test Generation • Results • Conclusions Texas Instruments (India)

Introduction Problem of finding a minimal test: • Static compaction cannot guarantee optimality. • Dynamic compaction is complex. • Solution: Target both faults F1 and F2 at the same time to find a single test. We define this as concurrent test generation. . . . T(F2) T(F1) Test set for fault F2 Test set for fault F1 v2 v1 v3 Texas Instruments (India)

Fault Classification T(F1) T(F1) = T(F2) T(F2) F1 and F2 are equivalent. F1 dominates F2. T(F1) T(F2) T(F1) T(F2) F1 and F2 are independent. F1 and F2 are concurrently testable. Texas Instruments (India)

Definitions Independent Faults4: Two faults are independent if and only if they cannot be detected by the same test vector. Concurrently-Testable Faults: Two faults that neither have a dominance relationship nor are independent, are defined as concurrently-testable faults. 4 S. B. Akers, C. Joseph, and B. Krishnamurthy, “On the role of Independent Fault Sets in the Generation of Minimal Test Sets,” in Proc. International Test Conf., 1987, pp. 1100-1107. Texas Instruments (India)

Structural Independences sa1 sa1 sa1 sa0 sa1 sa0 sa1 sa1 sa1 sa0 sa0 sa0 sa1 sa1 sa0 sa0 sa0 sa0 sa1 sa0 Functional Independences: Found by ATPG-like methods. Texas Instruments (India)

Example Circuit 2 4 a x 1 5 b 3 7 11 c y d 6 10 9 All faults are Stuck-at-1 type e 8 C17 - ISCAS85 Benchmark Circuit 1 R. K. K. R. Sandireddy and V. D. Agrawal, “Diagnostic and Detection Fault Collapsing for Multiple Output Circuits,” Proc. Design, Automation and Test in Europe (DATE) Conf., Mar. 2005, pp. 1014 - 1019. Texas Instruments (India)

Independence Matrix and Graph Clique C17 - ISCAS85 Benchmark Circuit Texas Instruments (India)

Independence Fault Collapsing A “similarity” based algorithm [2] collapses the independence graph: Highly Similar Highly Dissimilar Similarity of a fault-pair 5,11,7 1,8 3,9,2 4,6,10 C17 - ISCAS85 Benchmark Circuit Equiv. Indep. 2 A. S. Doshi and V. D. Agrawal, “Independence Fault Collapsing,” Proc. 9th VLSI Design and Test Symp., Aug. 2005, pp. 357 - 364. Texas Instruments (India)

Simulation-based Independence Fault Collapsing • The independence graph generation procedure [2] requires ATPG. • Here we present a new method for graph generation using simulation: • Start with a fully-connected independence graph for an equivalence collapsed fault set. • Simulation of random vectors without fault dropping removes edges between faults detected by the same vector. 2 A. S. Doshi and V. D. Agrawal, “Independence Fault Collapsing,” Proc. 9th VLSI Design and Test Symp., Aug. 2005, pp. 357 - 364. Texas Instruments (India)

Simulation-based Independence Fault Collapsing 301 74181 4-bit ALU Texas Instruments (India)

Simulation-based Concurrent Test Generation • For each group, generate all test vectors for the first fault in the group. • If the number of test vectors for a fault is large, use a subset (e.g., 250 maximum) of vectors. • Simulate all faults in the group to select one vector that detects most faults in that group. • If more vectors than one detect the same number of faults within the group, then select the vector that detects most faults outside the group as well. Texas Instruments (India)

74181 4-bit ALU Result Texas Instruments (India)

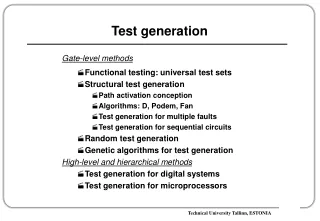

Results * Sun Ultra 5 *** Pentium Pro PC ** Hamzaoglu and Patel, IEEE-TCAD, 2000 Texas Instruments (India)

Number of Vectors for Increasing Circuit Sizes (100% Stuck-at Coverage) Single-fault ATPG (no compaction) Concurrent ATPG Minimum achieved! (dynamic compaction) Texas Instruments (India)

CPU Seconds for Increasing Circuit Sizes (100% Stuck-at Fault Coverage) Concurrent ATPG Minimum achieved! (dynamic compaction) Texas Instruments (India)

Conclusion • Concurrent test generation produces compact tests when combined with independence fault collapsing. • ATPG and set covering problems have exponential time complexities. Hence, we cannot expect absolute optimality for large circuits. • The concurrent ATPG procedure of this paper gives significantly smaller, and sometimes the optimum, test sets. • There is scope for improving the simulation-based algorithms for independence fault collapsing and concurrent test generation. Texas Instruments (India)

Thank You! Texas Instruments (India)