Logic Restructuring Using Range-Equivalent Circuits

210 likes | 347 Views

Logic Restructuring Using Range-Equivalent Circuits. Chih-Chung Wang. Outline. Background Range-Equivalent Circuit Node Merging and NAR Problem Formulation BSEC Problem and Example Future Work. Range-Equivalent Circuit. Range

Logic Restructuring Using Range-Equivalent Circuits

E N D

Presentation Transcript

Logic RestructuringUsing Range-Equivalent Circuits Chih-Chung Wang

Outline • Background • Range-Equivalent Circuit • Node Merging and NAR • Problem Formulation • BSEC • Problem and Example • Future Work

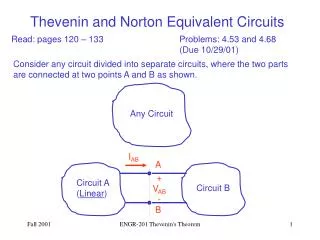

Range-Equivalent Circuit • Range • The range of a combinational circuit is the set of all possible output combinations. • Range-equivalent circuit • PI can be replaced without changing range

Node Merging • Replacing one node with another node by rewiring • Functionally equivalent, or functional differences are never observed at PO

Node Addition and Removal (NAR) • Add a node into the circuit to replace the target node • When more than one nodes is removed due to the addition of a new node, the circuit size is reduced

Problem Formulation • Given: Two bounded sequential logic circuits which both have k timeframes • Goal: Check the equivalence of these two circuits • Bounded Sequential Equivalence Checking (BSEC) • The timeframe k is too large to simplify the BSEC model directly or using node merging and NAR in short time

Bounded Sequential Equivalence Checking • Bounded sequential equivalence checking (BSEC) is a special case of SEC problems and simplifies the problem formulation by limiting the timeframes under verification to an affordable number.

Bounded Sequential Equivalence Checking • Linking every pair of corresponding primary outputs (POs) to one additional XOR gate • Then unfolded to a number of timeframes k to form the BSEC model: duplicated into k copies • All flop-flops (FFs) are removed and inputs of FFs in one timeframe are connected to corresponding signals at the next timeframe • One big OR gate takes the disjunction of every output

Bounded Sequential Equivalence Checking • In each time-frame, a flip-flop is translated into a pseudo primary input (PPI) and a pseudo primary output (PPO). • Each PPO value at one timeframe becomes the PPI value at the next timeframe.

Bounded Sequential Equivalence Checking • Since the BSEC model is combinational, its satisfiability can be answered by a Boolean SAT solver.

Bounded Sequential Equivalence Checking • Using NAR and node merging to simplify the combinational circuit can make checking speed up • However, in some cases, it would spend too much time.

Bounded Sequential Equivalence Checking • Assume we know that the equivalence was checked the same at the timeframe k-1. • If we want to checkthe equivalence at timeframe k, we only use the PPI, which is also the PPO of k-1, from the previous timeframe. • More precisely, the checking at k uses the range of PPO at k-1.

Bounded Sequential Equivalence Checking 0 … k-1 1 1 1

Problem • How can we make sure that using a range-equivalent circuit to replace the original circuit will remain the same equivalence?

Example • s27 • Range of PPOs • R={(0,0,0),(0,0,1), (0,1,0),(0,1,1), (1,0,0),(1,1,0)}

Example • s27 • Range of PPOs • R={(0,0,0),(0,0,1), (0,1,0),(0,1,1), (1,0,0),(1,1,0)} • Replacing with a simpler range-equivalent circuit

O = (PI1 + (-PI3) + X + Z) * (PI0 + (-Y) + Z) • O’ = PI0 + (PI1 * PI2) + (PI2 * (-PI3)) + (PI1 * (-X))) + ((-PI3) * (-X))) + ((-X) * (-Z)) + (Y * (-Z)) • (((PI1 + (-PI3) + X + Z) * (PI0 + (-Y) + Z)) * ((((-PI1) * (-X) * PI3) + ((-PI0) * Y)) * (-Z))) + (((((-PI1) * (-X) * PI3) + ((-PI0) * Y)) * (-Z)) * ((PI1 + (-PI3) + X + Z) * (PI0 + (-Y) + Z))) • (((-PI0’) * ((-PI1’) + (-PI2)) * ((-PI2’) + PI3) * ((-PI1’) + X) * (PI3’+ X) * (X + Z) * ((-Y) + Z)) * (PI0 + (PI1 * PI2) + (PI2 * (-PI3)) + (PI1 * (-X))) + ((-PI3) * (-X))) + ((-X) * (-Z)) + (Y * (-Z))) + ((PI0 + (PI1 * PI2) + (PI2 * (-PI3)) + (PI1 * (-X))) + ((-PI3) * (-X))) + ((-X) * (-Z)) + (Y * (-Z))) * ((-PI0’) * ((-PI1’) + (-PI2)) * ((-PI2’) + PI3) * ((-PI1’) + X) * (PI3’+ X) * (X + Z) * ((-Y) + Z)))

O = (PI1 + (-PI3) + X + Z) * (PI0 + (-Y) + ((-X) * Z)) • -O= ((-PI0) + (-PI1)) * ((-PI1) + Y) * ((-PI0) + PI3) * (PI3 + Y) * ((-PI0) + (-X)) * ((-X) + Y) * ((-PI0) + (-Z)) * (Y + (-Z)) * (X + (-Z)) • (((-PI0) + (-PI1)) * ((-PI1) + Y) * ((-PI0) + PI3) * (PI3 + Y) * ((-PI0) + (-X)) * ((-X) + Y) * ((-PI0) + (-Z)) * (Y + (-Z)) * (X + (-Z)) * (PI1 + (-PI3) + X + Z) * (PI0 + (-Y) + ((-X) * Z))) + (((-PI0) + (-PI1)) * ((-PI1) + Y) * ((-PI0) + PI3) * (PI3 + Y) * ((-PI0) + (-X)) * ((-X) + Y) * ((-PI0) + (-Z)) * (Y + (-Z)) * (X + (-Z)) * ((-PI0) + (-PI1)) * ((-PI1) + Y) * ((-PI0) + PI3) * (PI3 + Y) * ((-PI0) + (-X)) * ((-X) + Y) * ((-PI0) + (-Z)) * (Y + (-Z)) * (X + (-Z)))

Future Work • Reading papers to understand the algorithm of range-equivalent circuit, node merging and NAR • Studying the source code • Implementation